Fターム[5F102GQ01]の内容

接合型電界効果トランジスタ (42,929) | ヘテロ接合近傍の2次元キャリア層を導電路に利用するもの(H) (2,045) | 単一ヘテロ構造(電子) (1,860)

Fターム[5F102GQ01]の下位に属するFターム

電子供給層がチャネル層の下 (138)

Fターム[5F102GQ01]に分類される特許

41 - 60 / 1,722

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ、下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ、第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ、第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaNを用いた縦型の電界効果トランジスタにおいて、素子の作製にコストの上昇を招くことなく、ドレイン電流密度を大きくできるようにする。

【解決手段】GaNからなるチャネル層101と、GaNより大きなバンドギャップエネルギーを有してアルミニウムを含む窒化物半導体から構成されてチャネル層101の一方の面に形成された障壁層102を備える。ここで、チャネル層101の一方の面は、N極性面とされ、他方の面はIII族極性面とされていればよい。また、チャネル層101の他方の面に形成されたドレイン電極103と、ドレイン電極103に対向して障壁層102の上に形成されたゲート電極104と、ゲート電極104と離間して障壁層102の上に形成されたソース電極105とを備える。

(もっと読む)

窒化物半導体素子の製造方法

【課題】窒化珪素層を形成した場合でも、窒化物半導体層の転移密度を低減することができるとともに、窒化物半導体層の表面モフォロジーを優れたものとすることができる窒化物半導体素子の製造方法を提供する。

【解決手段】斜めファセットを有する第2の窒化物半導体層を有機金属気相成長法により形成する工程において、有機金属気相成長装置の成長室に供給されるIII族元素ガスに対するV族元素ガスのモル流量比が240以下である窒化物半導体素子の製造方法である。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】裏面電極と導通したパッドを破ることなく、複数のバイアホールの検査を短時間で実施できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、該基板の裏面に形成された裏面電極と、該基板を貫通するN個(Nは2以上の整数)のバイアホール16のそれぞれを経由して該裏面電極と電気的に接続されるように該基板の表面に形成されたN個のパッドと、該N個のパッドのそれぞれに電気的に接続されたN個のエピ抵抗30とを有する。そして、該N個のエピ抵抗を介して該N個のパッドと接続された配線34と、該配線と接続された検査用パッド36と、該N個のパッド、及び該N個のバイアホールを経由して該裏面電極に電流を流すように該基板の表面に形成された電流印加用パターンと、を備える。

(もっと読む)

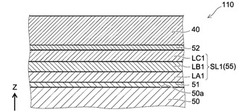

窒化物半導体基板

【課題】Si単結晶を下地基板として用いた場合の、リーク電流低減と電流コラプス改善が、効果的に達成された窒化物半導体基板を提供する。

【解決手段】Si単結晶基板Wの一主面上に窒化物からなる複数のバッファ層Bを介して窒化物半導体の活性層Cが形成されている窒化物半導体基板であって、バッファ層Bは少なくとも活性層Cと接する層50の炭素濃度が1E+18atoms/cm3以上1E+20atoms/cm3以下であること、バッファ層Bと活性層Cの界面領域80において全転位密度に対するらせん転位密度の比が0.15以上0.3以下であること、さらにバッファ層Bと活性層Cの界面領域80における全転位密度が15E+9cm−2以下である窒化物半導体基板。

(もっと読む)

印刷可能な半導体構造、並びに関連する製造方法及び組立方法

【課題】選択された物理的寸法、形状、組成、及び、空間的配置を有する高品質印刷可能半導体素子の製造、転写、組み立てのための高歩留りの経路を与える。

【解決手段】大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料処理を行う。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】ノーマリーオフ特性を具現すると共にゲートリーク電流を抑制する窒化物半導体素子及びその製造方法を提供する。

【解決手段】第1の窒化物層31とその材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、その上にオミック接触されたソース電極50と、これから離間して窒化物半導体30層上にオミック接触されたドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に、これらから離間して形成されたP型窒化物層40と、この上に形成されたN型窒化物層140と、ソース側の側壁が、P型窒化物層40及びN型窒化物層140のソース側の側壁と整列するようにN型窒化物層140上に接触させたゲート電極70とを含む。

(もっと読む)

高電子移動度トランジスタ

【課題】電子移動度を低下させることなく、電子密度を高くできる高電子移動度トランジスタを提供する。

【解決手段】Si基板100上に形成されたバッファ層10と、バッファ層10上に形成されたGaN層11と、GaN層11上に形成されたAlGaN層12と、AlGaN層12内に形成されると共に、互いに間隔をあけて形成されたソース電極13とドレイン電極14と、AlGaN層12上かつソース電極13とドレイン電極14との間に形成されたゲート電極15と、ソース電極13とドレイン電極14およびゲート電極15が形成されたAlGaN層12の一部を覆うように形成された絶縁膜16とを備える。上記絶縁膜16中にCsの原子が2×1013cm−2以上存在する。

(もっと読む)

半導体装置

【課題】高い障壁を有し、かつ高品質のバッファ層及びチャネル層を有する半導体装置を提供する。

【解決手段】基板10と、基板10上に設けられ、AlNからなる下地層12と、下地層12上に設けられ、AlxGa1−xNからなるバッファ層14と、バッファ層14上に設けられ、厚さが100nm以上300nm以下のGaNからなるチャネル層16と、チャネル層16上に設けられ、AlGaNからなる電子供給層20と、電子供給層20上に設けられたソース電極26、ドレイン電極28及びゲート電極30と、を具備し、バッファ層14のAlの組成xは、下地層12側の領域において0.3≦x≦0.5であり、チャネル層16側の領域において0.9≦x≦1.0である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、電極端における電界集中を緩和してデバイス特性の劣化を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を提供する。

【解決手段】HEMTは、SiC基板1上に、化合物半導体層2と、開口6bを有し、化合物半導体層2上を覆う、窒化珪素(SiN)の保護膜6と、開口6bを埋め込むように化合物半導体層2上に形成されたゲート電極7とを有しており、保護膜6は、その下層部分6aが開口6bの側面から張り出した張出部6cが形成されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】化合物半導体積層構造上の絶縁膜に所期の微細な開口を形成するも、リーク電流を抑止した信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2上にパッシベーション膜6を形成し、パッシベーション膜6の電極形成予定位置をドライエッチングにより薄化し、パッシベーション膜6の薄化された部位6aをウェットエッチングにより貫通して開口6bを形成し、この開口6bを電極材料で埋め込むように、パッシベーション膜6上にゲート電極7を形成する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁耐圧が高く、オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、前記第1の半導体層の上に形成された第2の半導体層14と、前記第2の半導体層の上に形成された第3の半導体層15と、前記第3の半導体層の上に形成されたゲート電極21と、前記第2の半導体層に接して形成されたソース電極22及びドレイン電極23と、を有し、前記第3の半導体層には、半導体材料にp型不純物元素がドープされており、前記第3の半導体層は、前記ゲート電極の端部より、前記ドレイン電極が設けられている側に張出している張出領域を有していることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

41 - 60 / 1,722

[ Back to top ]