Fターム[5F110AA08]の内容

Fターム[5F110AA08]に分類される特許

141 - 160 / 733

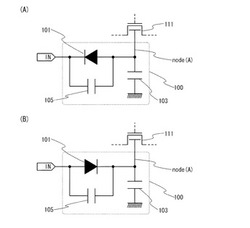

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

放射線撮像装置、放射線撮像表示システムおよびトランジスタ

【課題】被曝量による閾値電圧のシフトを抑制するが可能なトランジスタを提供する。

【解決手段】放射線撮像装置1は、フォトダイオードとトランジスタ111Bとを含む光電変換層を有する。トランジスタ111Bは、基板11上に、第1ゲート電極120A、第1ゲート絶縁膜129、半導体層126、第2ゲート絶縁膜130および第2ゲート電極120Bをこの順に有し、第1ゲート絶縁膜129および第2ゲート絶縁膜130におけるSiO2膜の総和が65nm以下となっている。トランジスタが被曝すると、ゲート絶縁膜におけるSiO2膜に正孔がチャージされ、閾値電圧がシフトし易くなるが、上記のようなSiO2膜厚の最適化により、閾値電圧シフトが効果的に抑制される。

(もっと読む)

半導体装置およびその作製方法

【課題】バックゲート電極、しきい値電圧を制御するための回路、および不純物添加法を用いずにしきい値電圧が制御されたトランジスタを作製する。該トランジスタを用いて、電気特性が良好で、信頼性が高く、消費電力の小さい半導体装置を作製する。

【解決手段】組成の制御された酸化タングステン膜を有するゲート電極を用いる。酸化タングステン膜の成膜方法によって組成などを調整され、仕事関数を制御することができる。仕事関数の制御された酸化タングステン膜をゲート電極の一部に用いることでトランジスタのしきい値を制御できる。しきい値電圧が制御されたトランジスタを用いることで、電気特性が良好で、信頼性が高く、消費電力の小さい半導体装置を作製することができる。

(もっと読む)

スパッタリングターゲット、スパッタリングターゲットの作製方法および半導体装置の作製方法

【課題】酸窒化物膜を作製する成膜技術を提供する。また、その酸窒化物膜を用いて信頼性の高い半導体素子を作製する。

【解決手段】窒化インジウム、窒化ガリウム、窒化亜鉛の少なくとも1つを原料の一とし、これと、酸化インジウム、酸化ガリウム、酸化亜鉛の少なくとも1つと混合して窒素雰囲気中で焼結したインジウムとガリウムと亜鉛を有する酸窒化物よりなるスパッタリングターゲットを用いて酸窒化物膜を作製することにより、必要な濃度の窒素を含んだ酸窒化物膜が得られる。得られた酸窒化物膜はトランジスタのゲートやソース電極、ドレイン電極等に用いることができる。

(もっと読む)

SOIウェハの製造方法

【課題】SOIウェハの支持基板ウェハの帯電を除去することのできるSOIウェハの製造方法を提供する。

【解決手段】活性層基板10と支持基板20との貼り合わせ面に酸化膜22を形成する酸化膜形成工程と、活性層基板10と支持基板20とを貼り合わせる貼り合わせ工程と、支持基板20に向けて活性層基板10に酸化膜22に達するまでのトレンチを形成するトレンチ形成工程と、トレンチから酸化膜22に向けて予め定められたイオンを注入するイオン注入工程と、トレンチ内部をポリシリコン3で充填する充填工程とを備える。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体膜、半導体素子、半導体装置およびそれらの作製方法

【課題】特性が安定した半導体膜を提供することを目的の一とする。または、特性が安定した半導体素子を提供することを目的の一とする。または、特性が安定した半導体装置を提供することを目的の一とする。

【解決手段】具体的には、絶縁性の表面に一方の面を接する第1の結晶構造を有する結晶を含む種結晶層(シード層)と、当該種結晶層(シード層)の他方の面に異方性の結晶が成長した酸化物半導体膜を有する構成とすれば良く、このようなヘテロ構造とすることにより、当該半導体膜の電気特性を安定化することができる。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】DRAMに、高純度化された、バンドギャップが2.5eV以上の酸化物半導体膜、炭化シリコン膜および窒化ガリウム膜などでなるトランジスタを用いることで、キャパシタの電位の保持期間が延びる。また、メモリセルが容量の異なるn個のキャパシタを有し、n個のキャパシタとそれぞれ異なるn本のデータ線を接続することによって保持容量を様々にとることができる。

(もっと読む)

帯電体並びにそれを用いた電界効果トランジスタ及びメモリ素子

【課題】 フローティングゲートメモリやMNOSメモリのような極薄膜の絶縁層を必要とせず、印刷、塗布でメモリ素子が製造可能となる簡便で、注入電荷量の制御が容易な帯電体、並びにこの帯電体をゲート絶縁膜に用いてFETを作製することにより、閾値電圧制御が可能で、長時間制御された閾値電圧状態を保持可能なFET及びメモリ素子を提供する。

【解決手段】 電荷注入が生じる電界強度(以降、電荷注入耐圧)および絶縁耐圧がそれぞれECI,HおよびEBHである絶縁体(以下,高電荷注入耐圧材料)と、その電荷注入耐圧ECI,LがECI,L < ECl,Hの関係にある絶縁体(以下、低電荷注入耐圧材料)の二種類の絶縁体を積層した絶縁物で、高電荷注入耐圧材料と低電荷注入耐圧材料のそれぞれに接し離れた2枚の電極にECI,L < |E| < EBH の電界強度で電圧を印加して低電荷注入耐圧材料側から電荷を絶縁体内に注入して帯電させる帯電体。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】薄膜トランジスタの半導体層に酸化物半導体を用いたとき、薄膜トランジスタのスイッチング特性およびストレス耐性が良好な薄膜トランジスタの半導体層用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、薄膜トランジスタの半導体層に用いられる酸化物であって、前記酸化物は、In、Ga、およびZnよりなる群から選択される少なくとも一種の元素と;Al、Si、Ni、Ge、Sn、Hf、Ta、およびWよりなるX群から選択される少なくとも一種の元素と、を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

ゲート絶縁材料、ゲート絶縁膜、および電界効果型トランジスタ。

【課題】高耐久性、高移動度、高オンオフ比であり、なおかつ低ターンオン電圧および低ヒステリシスを可能とするゲート絶縁材料、ゲート絶縁膜およびこれを用いた電界効果型トランジスタを提供すること。

【解決手段】ポリマーと金属化合物を含有するゲート絶縁材料であって、金属化合物が、マグネシウム化合物、亜鉛化合物、銅化合物、インジウム化合物、ランタニウム化合物、マンガン化合物、カルシウム化合物、スズ化合物、チタニウム化合物、ジルコニウム化合物、ハフニウム化合物の何れか1つ以上およびアルミニウム化合物とを含むことを特徴とするゲート絶縁材料。

(もっと読む)

有機素子材料

【課題】高温での処理を行わないで架橋させることが可能な有機素子材料を提供すること。

【解決手段】フッ素原子を含む基を有する繰り返し単位と、光二量化反応性基を有する繰り返し単位とを有する高分子化合物を含む有機薄膜トランジスタ絶縁層材料。フッ素原子を含む基の好ましい例は、水素原子がフッ素で置換されたアリール基、水素原子がフッ素で置換されたアルキルアリール基、特に水素原子がフッ素で置換されたフェニル基、水素原子がフッ素で置換されたアルキルフェニル基である。光二量化反応性基の好ましい例は、2位の水素原子がアリール基で置換されたビニル基、2位の水素原子がアリールカルボニル基で置換されたビニル基である。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

141 - 160 / 733

[ Back to top ]