Fターム[5F110AA08]の内容

Fターム[5F110AA08]に分類される特許

161 - 180 / 733

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造コストの削減が可能であるとともに、安定したトランジスタ特性を得ることが可能な薄膜トランジスタ回路基板及びその製造方法を提供する。

【解決手段】絶縁基板上に酸化物半導体薄膜を形成し、前記酸化物半導体薄膜の上にゲート絶縁層を形成し、前記ゲート絶縁層の上にゲート層を形成し、前記ゲート層の上にレジストパターンを形成し、前記レジストパターンをマスクとして、前記ゲート絶縁層及び前記ゲート層を一括してパターニングして、ゲート絶縁膜上にゲート電極を形成するとともに、ソース領域及びドレイン領域となる前記酸化物半導体薄膜を露出させ、露出させた前記酸化物半導体薄膜を、少なくともシラン(SiH4)を含むガスに晒し、前記シランを含むガスに晒した後に連続して層間絶縁膜を形成する、ことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

GaNベースの薄膜トランジスタの製造方法

【課題】電流特性と信頼性に優れ、閾値電圧が高いGaNベースの薄膜トランジスタを得ることができる製造方法を提供する。

【解決手段】GaNベースの薄膜トランジスタの製造方法は、n型GaNベースの半導体材を有する半導体エピタキシャル層を、基板上に形成する工程と、半導体エピタキシャル層上に絶縁体層を形成する工程と、絶縁体層上に、絶縁体層を部分的に露出するための開口部を有しているイオン注入マスクを形成する工程と、p型不純物を、開口部および絶縁体層を通してイオン注入して、n型GaNベースの半導体材の中にp型不純物がドーピングされた領域を形成し、その後、絶縁体層およびイオン注入マスクを除去する工程と、半導体エピタキシャル層上に誘電体層を形成する工程と、誘電体層を部分的に除去する工程と、ソース電極およびドレイン電極を形成する工程と、ゲート電極を形成する工程を含む。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバICの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジスタを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給する。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタのLSI製造後にしきい電圧の制御が可能で、かつ、回路面積を増大させず、かつ信頼性に優れるという特徴を有する技術を提供する。

【解決手段】シリコン半導体支持基板1の上面に設けられた積層膜(3nm以上4nm以下の第1のシリコン酸化膜2/0.3nm以上2nm以下のシリコン窒化膜3/5nm以上10nm以下の第2のシリコン酸化膜4/3nm以上20nm以下の膜厚)を有するSOI層5と、上記構造に所定の間隔を介して互いに対向して設けられたソース・ドレイン拡散層6と、当該ソース拡散層とドレイン拡散層の間の上記半導体基板の表面上に形成されたゲート絶縁膜7と、上記ゲート絶縁膜の上に形成されたゲート電極8を具備してなる電界効果型半導体装置において、シリコン支持基板1から電圧を印加することにより、直接トンネル効果によって電荷をシリコン窒化膜3に一定時間保持してしきい電圧を調整する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】同一の極性を有する複数の薄膜FETの閾値電圧に差をつけて、半導体装置の性能の最適化を図ることができる。

【解決手段】半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に形成された薄膜n型FET100と、埋め込み絶縁膜2上に形成された薄膜p型FET101と、埋め込み絶縁膜2上に形成された薄膜n型FET100bと、薄膜n型FET100のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4と、薄膜p型FET101のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域5と、薄膜n型FET100bのチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4bと、を備え、p型ウェル領域4、4b、5は、n型ウェル領域40によって囲まれており、かつ互いに接触していない。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】マスク数が少なく、工程が簡略な半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜と、半導体膜と、不純物半導体膜と、導電膜と、をこの順に積層して形成し、導電膜を加工してソース電極及びドレイン電極を形成し、不純物半導体膜を離間させつつ半導体膜の上部を加工してソース領域及びドレイン領域と、ソース領域及びドレイン領域と重畳しない部分の上部が除去された半導体層と、を形成し、ゲート絶縁膜、半導体層、ソース領域及びドレイン領域、ソース電極及びドレイン電極上にパッシベーション膜を形成し、パッシベーション膜上にエッチングマスクを形成し、エッチングマスクにより、ソース電極またはドレイン電極に達する開口部を形成しつつ、少なくともパッシベーション膜と半導体層を島状に加工し、エッチングマスクを除去し、ゲート絶縁膜及びパッシベーション膜上に画素電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体用ターゲットに含まれる複数種の原子の原子量の違いを利用し、原子量の小さい亜鉛を優先的に酸化物絶縁膜に堆積させ、亜鉛を含む種結晶を形成すると共に、種結晶上に原子量の大きいスズ、インジウム等を結晶成長させつつ堆積させることで、複数の工程を経ずとも、結晶性酸化物半導体膜を形成することを要旨とする。さらには、種結晶として、六方晶構造の亜鉛を含む結晶を有する種結晶を核として、結晶成長させて結晶性酸化物半導体膜を形成することで、単結晶、または実質的に単結晶である結晶性酸化物半導体膜を形成することを要旨とする。

(もっと読む)

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

スパッタリングターゲットおよび半導体装置の作製方法

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。また、その酸化物半導体膜を用いた信頼性の高い半導体素子を作製する方法を提供することを課題の一とする。

【解決手段】成膜に用いるスパッタリングターゲットの中の不純物であるアルカリ金属、アルカリ土類金属、及び水素を排除することにより得られる新規なスパッタリングターゲットを用いれば、これらの不純物の含有量の少ない酸化物半導体膜を成膜することができる。

(もっと読む)

有機薄膜トランジスタ絶縁層用組成物及び有機薄膜トランジスタ

【課題】大気中で駆動する場合の閾値電圧の絶対値が小さい有機薄膜トランジスタを製造しうる有機薄膜トランジスタ絶縁層用組成物を提供すること。

【解決手段】分子内に環状エーテル構造を有する基を含有する化合物(A)と、含フッ素溶媒(B)とを含む有機薄膜トランジスタ絶縁層用組成物。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】結晶性半導体膜に対する非晶質半導体膜のエッチング選択比が高いエッチング方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、Br系ガスと、F系ガスと、酸素ガスの混合ガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを行うことで、露出された部分の膜減りを抑えることができる。更には、当該エッチング方法を薄膜トランジスタのバックチャネル部を形成するエッチングに採用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。該薄膜トランジスタ上には絶縁層が設けられていることが好ましい。

(もっと読む)

アクティブマトリクス型有機EL表示装置およびその駆動方法

【課題】アクティブマトリクス型有機EL表示装置の表示領域にある薄膜トランジスタの信頼性を高めることにある。

【解決手段】

アクティブマトリクス型有機EL表示装置は、マトリクス状に配置された複数の画素を有する表示領域と、駆動回路を有する周辺領域と、を備える。さらに、アクティブマトリクス型有機EL表示装置の前記画素は、ボトムゲート型の第1トランジスタと、カソード電極と、アノード電極と、カソード電極およびアノード電極の間に設けられた有機EL層と、を有し、前記駆動回路は、ボトムゲート型の第2トランジスタと前記第2トランジスタ上に設けられたバックゲート電極とを有する。前記画素が最低輝度を表示する際に、前記第1トランジスタのゲート電位は前記カソード電極の電位よりも低い。

(もっと読む)

有機薄膜トランジスタ用化合物及びそれを用いた有機薄膜トランジスタ

【課題】酸化安定性と塗布プロセスが適用可能な溶解性を有する有機薄膜トランジスタ用化合物を提供する。

【解決手段】下記式(1)で表わされる有機薄膜トランジスタ用化合物。 (もっと読む)

(もっと読む)

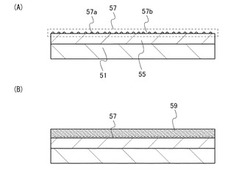

カレントミラー回路、電流生成回路及び発光装置

【課題】負荷に供給する電流を精度よく出力する。

【解決手段】ゲート電極とドレイン電極が短絡されている第1トランジスタTr1と、第1トランジスタTr1のゲート電極に、ゲート電極が接続された第2トランジスタTr2と、を備えるカレントミラー回路10において、第1トランジスタTr1と第2トランジスタTr2は、絶縁膜12を介してゲート電極1の上部に設けられてチャネル領域が形成される半導体膜2と、半導体膜2上のチャネル領域を覆う領域に設けられる保護膜3と、半導体膜2のチャネル領域を挟む一対の端部に離間して設けられるとともに保護膜3の一部に重なって設けられソース電極6及びドレイン電極7とをそれぞれ有するとともに、少なくとも第2トランジスタTr2は、ソース電極6の保護膜3に対するチャネル長方向への重なり長がドレイン電極7の保護膜3に対する重なり長より長い構造を有する。

(もっと読む)

電子装置とその作製方法およびスパッタリングターゲット

【課題】絶縁性酸化物の量産性を高めこと、また、そのような絶縁性酸化物を用いた半導体装置に安定した電気的特性を付与すること、信頼性の高い半導体装置を作製する。

【解決手段】亜鉛のように400〜700℃で加熱した際にガリウムよりも揮発しやすい材料を酸化ガリウムに添加したターゲットを用いて、DCスパッタリング、パルスDCスパッタリング等の大きな基板に適用できる量産性の高いスパッタリング方法で成膜し、これを400〜700℃で加熱することにより、添加された材料を膜の表面近傍に偏析させる。膜のその他の部分は添加された材料の濃度が低下し、十分な絶縁性を呈するため、半導体装置のゲート絶縁物等に利用できる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の優れたトランジスタを作製する。

【解決手段】基板上に酸化物絶縁膜を形成し、該酸化物絶縁膜上に酸化物半導体膜を形成した後、酸化物半導体膜に含まれる水素を除去させつつ、酸化物絶縁膜に含まれる酸素の一部を脱離させる温度で加熱した後、該加熱された酸化物半導体膜を所定の形状にエッチングして島状の酸化物半導体膜を形成し、島状の酸化物半導体膜上に一対の電極を形成し、該一対の電極及び島状の酸化物半導膜上にゲート絶縁膜を形成し、該ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

161 - 180 / 733

[ Back to top ]