Fターム[5F110AA24]の内容

Fターム[5F110AA24]の下位に属するFターム

シミュレーション (22)

Fターム[5F110AA24]に分類される特許

81 - 100 / 180

センサアレイ

【課題】多数のセンサを配列しているセンサアレイを任意の大きさに切断して使用する場合に、切断されたセンサアレイ上に配置されている各センサが正常であるかどうかを容易に区別することができるセンサアレイを提供する。

【解決手段】互いに平行に配置された複数の選択線11と、前記選択線11と交差する方向に互いに平行に配置された複数のデータ線12と、前記複数の選択線11と前記複数のデータ線12とで囲まれた各領域に配置され、前記選択線11及び前記データ線12と接続された複数のセンサ13と、前記複数のセンサ13のそれぞれの周囲に配置された切断検出線14とを有する。

(もっと読む)

半導体デバイスの製造方法

【課題】半導体デバイスの製造工程における生産性の向上を図ることができる半導体デバイスの製造方法を提供することを目的としている。

【解決手段】準備したSOIウエハに半導体機能素子及び前記SOIウエハを構成する支持基板に接続するための基板コンタクトを形成し、前記半導体機能素子上に形成した外部接続パッド同士が非接続となるように前記基板コンタクトと前記外部接続パッドと接続するパターンを形成し、前記外部接続パッド間の導電度を測定する半導体デバイスの製造方法。

(もっと読む)

TFTアレイ検査装置

【課題】従来構成のアレイ検査装置では検出することができない基板の欠陥についても検出可能とする。

【解決手段】電子線を基板に照射して得られる2次電子をエネルギー選別して検出することにより基板の欠陥を検出するTFTアレイ検査装置において、エネルギー選別を行うエネルギーフィルタと、エネルギーフィルタを通過した2次電子を検出する2次電子検出器とを備え、エネルギーフィルタは少なくとも2枚のグリッドを有し、この各グリッドに異なる電圧を印加する。

(もっと読む)

電界分布又はキャリア分布を高次高調波の強度に基づいて検出する検出装置及びその検出方法

【課題】 従来、サンプル中における電荷分布の変化自体を直接的に観察することはできなかった。

【解決手段】 電極間における電界分布又はキャリア分布を高次高調波の強度に基づいて検出する検出装置100であって、ペンタセンFET50に基本波を照射する照射部1と、ペンタセンFET50における電圧印加時の電界分布又はキャリア分布に応じて生成された前記高次高調波を検出する検出部15と、第1信号に基づき前記照射部よりペンタセンFET50に前記基本波を照射させ、第2信号に基づきペンタセンFET50に電圧を印加する制御信号出力部30と、を備え、制御信号出力部30は、前記第1信号の出力時点と前記第2信号の出力時点との間の時間間隔を変更可能に構成される。

(もっと読む)

表示装置およびその製造方法ならびに検査装置および検査方法

【課題】隣接する映像信号線間の短絡を発見しやすくした検査用画像を表示する表示装置を提供する。

【解決手段】本表示装置は、映像信号線時分割駆動方式のアクティブマトリクス型液晶表示装置であって、映像信号線駆動回路300により、1水平期間毎に各映像信号線Lsを介して各画素形成部Pxへ白輝度または黒輝度に対応する画素値が書き込まれ、液晶パネル500には、表示画面の縦方向に延びており一列毎に一列分の間を空けて配列される図中の「○」の記号で示される直線群(縦縞模様)が表示される。ここで、上記映像信号線時分割駆動方式の表示装置は隣接する映像信号線間の短絡が生じやすく、この短絡が生じた異常部分は、直線群の中で3列分の太さを有する直線として表示されるので、容易に上記異常部分を発見することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 完全空乏型SOIトランジスタを有する半導体装置において、ウエハ面内の閾値を安定化さることが可能な半導体装置の高歩留安定化システムを提供する。

【解決手段】 完全空乏型SOIトランジスタを有する半導体装置において、チャネルドープ量の異なる2つのSOINMOSトランジスタを並列に接続し、ヒューズトリミングで選択できることを特徴とする。

(もっと読む)

基板ダイオードを備えてプロセス耐性構造を有するSOIデバイス及びその製造方法

適切に設計された製造フローに従ってSOIデバイス(200、300)の基板ダイオードが形成され、ダイオード特性に実質的に影響を及ぼすことなく、トランジスタの性能を強化するメカニズムが実装される。一形態では、基板ダイオードの各々の開口部(211A、211B、311A、311B)は、ドレインおよびソース領域(237、337)を画定するために用いられる対応のサイドウォールスペーサ構造(236、336)を形成後に形成され、これにより、ダイオード領域において、側方向に著しくドーパントが拡散する。これにより、トランジスタデバイス(230A、230B、330A、330B)のスペーサ(236、336)除去に基づく後続のシリサイデーションシーケンスの間、プロセスマージンが十分に与えられる。さらなる形態では、これに加えて、あるいはこれに代えて、各々のトランジスタデバイス(230A、230B、330A、330B)の構造に実質的に影響を及ぼさずに、オフセットスペーサ(360S)が形成される。  (もっと読む)

(もっと読む)

アレイ基板、並びに、アレイ基板及び液晶パネルの検査方法

【課題】検査時間が短縮されたアレイ基板、及び、検査時間が短縮されたアレイ基板の検査方法を実現する。

【解決手段】本発明のアレイ基板11は、各絵素60には、絵素電極70に接続された第1スイッチング素子41と、第2スイッチング素子46とが設けられており、第1スイッチング素子41と第2スイッチング素子46とが、各々異なるゲート線26・27及びソース線22・23に接続されている。

(もっと読む)

SOIトランジスタの評価方法および評価装置

【課題】 SOI MOSFETのAC動作時の実効的な寄生容量を精度良く測定可能な評価方法とMOSFET作製後のSOI基板の品質評価方法およびそれらの評価装置を提供する.

【解決手段】SOI MOSFETのゲートバイアスに交流信号を重乗し,ドレイン電流の応答から,ロックインアンプを用いて実効寄生容量を測定する.SOI MOSFETのバックゲートバイアスや試料温度が異なる条件で実効寄生容量を測定して比較するとSOI層と埋め込み酸化膜(BOX層)との界面の品質を評価できる.

(もっと読む)

ウェル電位トリガによるESD保護

【課題】ESD保護を可能にするための集積回路を提供すること。

【解決手段】集積回路は、基板領域、ソース、ドレイン、およびソース領域とドレイン領域の間に配設されたチャネル領域上に形成されたゲート領域を有する少なくとも1つのインターリーブされたフィンガーを有するトランジスタ・デバイスを含む。トランジスタ・デバイスはさらに、基板領域の電位を測定するためのソース領域に隣接して形成された少なくとも1つの高濃度ドープ接合を含む。集積回路はさらに、少なくとも1つの高濃度ドープ接合に結合されたスイッチング回路を含み、電位をスイッチング回路に転送して、全ESD電流を流すよう、または全ESD電流が流れるようにトリガするようになっている。

(もっと読む)

薄膜トランジスタ、その製造方法及びこれを具備した有機電界発光表示装置

【課題】SGS結晶化法で非晶質シリコン層を多結晶シリコン層に結晶化する場合、多結晶シリコン層が特定なラマンスペクトラムのピーク値を有する薄膜トランジスタ、その製造方法及びこれを備えた有機電界発光表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、前記基板上に位置し、ソース/ドレイン領域及びチャネル領域でなっていて、多結晶シリコーン層で形成された半導体層と、前記半導体層の一定領域に対応するように位置したゲート電極と、前記半導体層とゲート電極間に位置したゲート絶縁膜と、前記半導体層のソース/ドレイン領域と電気的に連結されているソース/ドレイン電極とを含み、前記多結晶シリコーン層は相異なるラマンスペクトラムのピーク値を有する複数個の領域を含むことを特徴とする。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難いゲート絶縁膜、かかるゲート絶縁膜の評価方法を提供する。

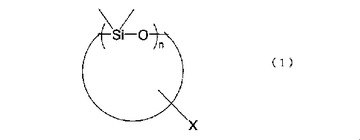

【解決手段】ゲート絶縁膜3は、下記一般式(1)で表される構造を有しており、下記一般式(1)で表される構造中のnが3または4であるものの総数をAとし、nが5以上であるものの総数をBとしたとき、{A/(A+B)}×100が1.2%以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

[式中、nは2以上の整数を表す。また、Xは水素原子または水酸基を表す。]

(もっと読む)

評価装置およびその評価装置を用いた評価方法

【課題】 非晶質シリコン膜をレーザー光により結晶化した多結晶シリコン膜を用いた薄膜トランジスタを備えた表示装置においては、表示品質の点で、基板面内における多結晶シリコン膜の粒径のばらつきを低減することが必要となる。しかし、多結晶シリコン膜の表面の凹凸を光学的に管理する方法では、ミクロレベルのばらつきしか把握できない。

【解決手段】 本発明にかかる評価装置においては、複数の評価セル101と、評価セル101に電圧を印加する信号配線105と、評価セル101からの出力を信号取り出し配線106を介して測定するための信号取り出し配線用出力端子パッド104とを絶縁性基板1上に備えているので、電気特性の面内分布を容易に測定できる。また、多結晶シリコン膜の結晶粒径と関連する電気特性を評価することにより、多結晶シリコン膜の結晶粒径の面内ばらつきを管理できる。

(もっと読む)

結晶化率の測定方法及び測定装置

【課題】精度良く、かつ短時間に、半導体薄膜の結晶化率を測定する方法を提供する。

【解決手段】基体上に形成された半導体薄膜に、半導体薄膜と基体との間に光学的干渉共鳴を起こす波長を含む光L2を照射し、光の透過光L3の光強度、或いは、光の反射光の光強度を、測定することにより、半導体薄膜の結晶化率を測定する。

(もっと読む)

半導体装置の製造方法

【課題】高圧水蒸気アニール処理等のアニール処理工程を、過不足なく適正化できるようにし、これによって良好な特性の半導体装置を製造することのできる方法を提供する。

【解決手段】膜質改善処理のためのアニール処理工程を備えた半導体装置の製造方法である。基板1の、TFT8の形成領域とは異なる領域に、アニール処理によって光学定数が変化する光学定数可変材料からなるモニタ膜10を形成する工程と、アニール処理工程の後、モニタ膜10の光学定数の変化を検出し、アニール処理が、膜質改善処理として予め設定した適正範囲になっているか否かを評価する工程と、を備えている。

(もっと読む)

液晶ディスプレイ薄膜トランジスターアレイ基板の検査設備とその検査方法

【課題】光電効果の薄膜トランジスターに対する影響を早期に検出し、製品の信頼性および工程に関連する問題を早期に反映させることのできる検査方法を提供する。

【解決手段】液晶ディスプレイ薄膜トランジスターアレイ基板の欠陥を検査することに適用する検査方法であって:検査設備を提供することであり、前記検査設備がシャンバー、前記シャンバー中に配置されるプラットホーム、発光機構および電気特性テスト機構を含むものと;前記液晶ディスプレイ薄膜トランジスターアレイ基板をプラットホーム上に載置することと;前記発光機構を利用して前記液晶ディスプレイ薄膜トランジスターアレイ基板を照射することと;前記電気特性テスト機構を利用して前記発光機構の照射を経た前記液晶ディスプレイ薄膜トランジスターアレイ基板の電気特性を検査することとを含むものである。

(もっと読む)

液晶表示パネルの製造方法及び液晶表示パネル

【課題】検査用端子の高さを高くしてプローブとの間の接触性が良好となるようにした液

晶表示パネルの製造方法及び液晶表示パネルを提供すること。

【解決手段】本発明の液晶表示パネルは、第1の検査用端子形成位置に順次形成された第

1の導電性材料からなる膜62a、第1の絶縁膜63、半導体材料からなる膜34b、第

2の導電性膜32a、第2の絶縁膜39、第1のコンタクトホール66を介して第1の導

電性膜62aと電気的に接続された第1の検査用端子67と、第1の絶縁膜63上の第2

の検査用端子形成位置に順次形成された半導体材料からなる膜34c、第2の導電性材料

からなる膜64a、第2の絶縁膜39、第2のコンタクトホール68を介して第2の導電

性材料からなる膜64aと電気的に接続された第2の検査用端子69と、を備えることを

特徴とする。

(もっと読む)

半導体装置の評価方法

【課題】電界効果型トランジスタ及び薄膜トランジスタにおける、閾値電圧の変動の要因となっている層を判別する。

【解決手段】電界効果型トランジスタ及び薄膜トランジスタにおいて、閾値電圧の変化は、回路の誤作動を招く。閾値電圧が変化する主な要因として、絶縁層中又は絶縁層と半導体層の界面における、電荷のトラップが考えられる。負荷前後の閾値電圧とフラットバンド電圧が一定の範囲内に存在するか否かにより、電荷が絶縁層にトラップされているか、半導体層と絶縁層の界面にトラップされているかを判別する方法を提供する。

(もっと読む)

電気光学装置及び検査方法

【課題】フォトリソグラフィー法で使用される露光装置等、電気光学装置の製造に使用さ

れる装置の解像度等の計時変化を検知することが可能な電気光学装置及び検査方法を提供

すること。

【解決手段】本発明の電気光学装置は、第1電極と第2電極が平行配置された電極対であ

って、前記第1電極と前記第2電極の間隔が前記電極対毎に異なっている複数組の電極対

(51a〜51f)と、共通端子53と、複数個の個別端子55a〜55fと、前記複数

組の電極対のうちの一方側の電極と前記共通端子との間を接続するための第1配線52a

〜52fと、前記複数組の電極対のうちのそれぞれの他方側の電極と前記複数個の個別端

子との間を接続するための第2配線54a〜54fとを備えたことを特徴とする。

(もっと読む)

TFTアレイ検査における電子線走査方法

【課題】1ピクセル当たりの電子線のサンプリング点数を減少させるとともに、ピクセルに照射する電子線の照射位置精度の低下を抑制する。

【解決手段】電子線照射によるTFTアレイの欠陥検査において、TFTアレイの各ピクセルに照射する電子線の走査方法であり、各ピクセル内における電子線の走査方向を実質的に対角方向とすることで、1ピクセル当たりの電子線のサンプリング点数を減少させるとともに、ピクセルに照射する電子線の照射位置精度の低下を抑制する。電子線をTFTアレイのソース方向およびゲート方向に走査して、各ピクセルに電子線を照射するとともに、TFTアレイのソース方向およびゲート方向の少なくとも何れか一方の方向の電子線走査において、ピクセルピッチで照射を行うとともに、隣接する走査ライン間において電子線の照射位置をオフセットさせる。

(もっと読む)

81 - 100 / 180

[ Back to top ]