Fターム[5F110AA24]の内容

Fターム[5F110AA24]の下位に属するFターム

シミュレーション (22)

Fターム[5F110AA24]に分類される特許

41 - 60 / 180

薄膜トランジスタ基板の検査方法及び検査装置、並びに表示パネルの製造装置

【課題】微結晶シリコンを用いた薄膜トランジスタ基板において、基板の良否判断を確実に行う。

【解決手段】微結晶シリコンを用いた薄膜トランジスタを備えた薄膜トランジスタ基板の検査装置60aであって、薄膜トランジスタのゲート電圧−ドレイン電流の特性を測定するための特性測定部Mと、特性測定部Mで測定されたゲート電圧−ドレイン電流の特性曲線のオフ電流部分におけるドレイン電流の大きさ、及びドレイン電流が最小のときのゲート電圧の大きさに基づいて、薄膜トランジスタの良否を判断するための良否判断部Jとを備えている。

(もっと読む)

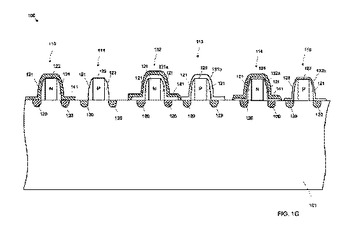

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

アクティブマトリクス基板及びその検査方法

【課題】画素電極を形成した後の静電気対策及びアレイ検査の双方を実現する。

【解決手段】マトリクス状に設けられた複数の画素電極20aと、各画素電極20aの整列方向の一方向に沿って互いに平行に延びるように設けられた複数の表示用配線18aと、各表示用配線18aの端部にそれぞれ設けられた複数の入力端子20cと、各入力端子20cに導通可能に設けられた短絡配線20bとを備え、各入力端子20cに重なるように圧電素子6aが設けられ、各入力端子20cと短絡配線20bとの間には、短絡配線20bが帯電したときに各入力端子20cと短絡配線20bとを導通状態にすると共に、各入力端子20cが押圧されたときに圧電素子6aからの電気信号により各入力端子20cと短絡配線20bとを非導通状態にするスイッチング素子8aがそれぞれ設けられている。

(もっと読む)

半導体薄膜の形成方法および半導体薄膜の検査装置

【課題】レーザアニールによる結晶化を利用した半導体薄膜の形成において、その結晶化度を従来よりも高精度に評価することが可能な半導体薄膜の形成方法を提供する。

【解決手段】p−Si膜23の結晶化度の検査処理の際に、p−Si膜23およびa−Si膜230へ向けて、LED12によって照射光Loutを照射する。これにより、p−Si膜23およびa−Si膜230の干渉縞画像(干渉縞画像データD1)を取得する。また、画像処理用コンピュータ15において、p−Si膜23(結晶化領域51)とa−Si膜230(未結晶化領域50)との(反射)光学的段差を求める。そして求めた(反射)光学的段差に基づいて、p−Si膜23に対する選別および結晶化度の制御量の算出のうちの少なくとも一方の評価を行う。これにより、従来よりも確実な選別が実現されると共に、新たな制御(結晶化度の制御)が実現可能となる。

(もっと読む)

液晶モジュール及び光電流の測定方法

【課題】従来技術では長期間の経時変化に対応できず、また薄膜トランジスタの照度を測定するためのフォトセンサとして利用する場合、精度が低くすぎフォトセンサとして使用は困難であった。薄膜トランジスタの照度を測定するためのフォトセンサを利用する場合に、長期間に渡る経時変化を1%以下に抑え、小型高精度かつフォトセンサの出力の調整が出来るフォトセンサ回路及び液晶モジュールを提供する。

【解決手段】フォトセンサのソース電極に交流電圧を印加して、ソース電極からドレイン電極に向かって流れる電荷と、前記薄膜トランジスタのドレイン電極からソース電極に向かって流れる電荷が、ほぼ等しくなるように駆動するようにした。また、それに伴い薄膜トランジスタが有する光感度及び光応答性の個体差を修正する機構を加えた。

(もっと読む)

電気光学装置の製造方法及び電気光学装置

【課題】電気特性のバラツキが少ないTFTを備えた電気光学装置の製造方法及び電気光

学装置を提供すること。

【解決手段】本発明の電気光学装置10の製造方法は、表示領域12の周囲の少なくとも

1箇所に、TFTの製造時に、同時に、同条件で、同じ層構造の半導体層を備える膜厚測

定用素子X部分を形成する工程と、前記TFTのチャネルエッチング時に前記膜厚測定用

素子X部分の半導体層も同時にエッチングする工程と、得られた膜厚測定用素子Xの半導

体層の膜厚を測定することによって前記TFTのチャネル領域の半導体層の膜厚を求める

工程と、を備えることを特徴とする。

(もっと読む)

被検査基板、被検査基板の製造方法並びに欠陥検査装置

【課題】隣接するパターンと比較して、一致しない場合を不良として検出する方法が知られている。この方法を用いることで、拡大倍率の若干の誤差等の偽信号を抑制できる。しかし、この技術を用いるためには、同じパターンが繰り返された繰り返しパターンが要求される。そのため、アドレス番号等個別パターンを有するものには適用できず、上記した技術を用いることができるパターンは限られたものになるという課題があった。

【解決手段】アドレス番号部13(個別パターン)の情報を隣接するパターンと同形状の遮蔽層20で覆うことで個別情報を遮蔽し、繰り返しパターン14とアドレス番号部13とを合成した新たな繰り返しパターン14Aとして扱った。繰り返しパターンは、高速、高精度で欠陥検出が可能である。そのため、個別パターンを内包するパターンに対しても高速、高精度に欠陥検出し得る被検査基板を提供可能とした。

(もっと読む)

分子検出素子及びシステム

【課題】絶縁体層への吸着分子の比較的弱い相互作用(物理吸着)と誘電性を検出する機能を利用することにより、脱離性や繰り返し性を向上させることと、検体ガスの種類とその濃度を同時的に検出する事を可能にする。

【解決手段】本発明は、金属層、絶縁体層、半導体層より構成されるMISキャパシタ構造、或いは該MISキャパシタ構造を含む電界効果トランジスタFETを利用する。絶縁体層は、多数の貫通型細孔を設けた電気的に不活性な材質製の基板に分子吸着性絶縁層を塗膜して形成する。絶縁体層の一方の側に半導体層を、かつ他方の側に金属層を形成すると共に、貫通型細孔を通して検出すべきガス或いは液体が通過できるように構成する。

(もっと読む)

トランジスタ構造のバイオセンサー及びその製造方法

【課題】抗原−抗体反応を感知するアクティブポリマーと親水性ナノ粒子を使用してトランジスタのチャネル領域を形成することによって、抗原−抗体間の反応性と親水性を増加させて、センサーの特性を改善させたトランジスタ構造のバイオセンサーを提供する。

【解決手段】バイオセンサー100は、基板101上に形成されたゲート電極102と、ゲート電極上に形成されたゲート絶縁膜103と、ゲート絶縁膜上に形成されたソース電極及びドレイン電極104と、ソース電極及びドレイン電極の間に形成されたチャネル領域と、を備え、チャネル領域は、抗原−抗体反応を感知するアクティブポリマー及び親水性ナノ粒子を使用して形成されたアクティブ層105を含む。アクティブ層は、直接印刷技術を利用して大面積工程が可能であり、プラスチックのような多様な基板の上に素子の製作が容易である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

酸化物半導体層の非破壊検査方法、及び酸化物半導体層の作製方法

【課題】薄膜トランジスタの活性層などとして有用な非晶質又は多結晶性の酸化物半導体層の膜質を、非破壊で迅速に調べることのできる検査方法、及び、その検査方法を活用した非晶質又は多結晶性の酸化物半導体層の作製方法を提供すること。

【解決手段】検査しようとする非晶質又は多結晶性の被検査酸化物半導体層に対して励起光2を照射し、被検査酸化物半導体層から放出される光のうち、バンドギャップエネルギーに対応する波長よりも長い波長領域のフォトルミネッセンス光4の強度を測定する。そして、被検査酸化物半導体層と同じ工程で作製され、被検査酸化物半導体層と同じ元素組成と膜厚とを有する、非晶質又は多結晶性の参照用酸化物半導体層に対し、同じフォトルミネッセンス光強度の測定と、膜質の測定とを行い、フォトルミネッセンス光強度と膜質との関係を得て、この関係に基づいて酸化物半導体層の膜質を推定する。

(もっと読む)

半導体装置の製造方法及びこれに用いるSOQ基板

【課題】SOQ基板上のクラックを容易に検出可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】本発明に係る半導体装置の製造方法は、石英基板の上に半導体層を形成してなるSOQ基板を準備する工程と;前記SOQ基板上に、複数の半導体装置形成領域とクラック検査用のパターンを形成する工程と;前記パターンを観察し、当該パターンにクラックが発生しているか否かを検査する第1の検査工程と;前記第1の検査工程の結果、前記パターンにクラックが発生している場合には、前記半導体装置形成領域内のクラックを検査する第2の検査工程とを含むことを特徴とする。

(もっと読む)

薄膜トランジスタのオン電流低下度を予測する方法

【課題】SIMSにおける積層膜の深さ方向測定時に積層膜界面の帯電による強度低下を利用し薄膜トランジスタの特性を予測する方法を提供。

【解決手段】薄膜トランジスタの積層構造と同じ積層構造で、それぞれ、オン電流が異なる複数の試料に対し、表面帯電状態を非中和にした状態で1次イオン照射し飛散した2次イオンにより深さ方向プロファイルを作成する第1工程と、プロファイルに基づいてシリコンの2次イオン強度の低下率を求める第2工程と、2次イオン強度の低下率とオン電流低下度の相関曲線を作成する第3工程と、第1及び第2工程の手順により半導体層界面前後におけるシリコンの2次イオン強度の低下率を求める第4工程(S2,S5)と、第4工程において求められた試料の2次イオン強度の低下率を、シリコンの2次イオン強度の低下率とオン電流低下度の相関曲線に照らして試料のオン電流低下度を求める(S6)。

(もっと読む)

半導体装置

【課題】製造工程を変更することなくMOSトランジスタのドレイン電流−温度特性を制御する。

【解決手段】半導体層1に互いに間隔をもって形成されたソース11s及びドレイン11d,13dと、ソース11sとドレイン11d,13dの間の半導体層1上にゲート絶縁膜5を介して形成されたゲート電極7とをもつMOSトランジスタを備えている。MOSトランジスタで、ソース11sは上方から見てゲート電極7とは間隔をもつ位置に形成されている。ドレイン13dは上方から見てゲート電極7に一部重複する位置に形成されている。上方から見たソース11sとゲート電極7の間の距離AはMOSトランジスタが温度上昇に対してドレイン電流が増加するドレイン電流−温度特性をもつ寸法に設定されている。

(もっと読む)

デバイス検査方法

【課題】 保護膜に欠陥のあるデバイスと保護膜に欠陥のないデバイスを選別することができるデバイス検査方法を提供すること。

【解決手段】 固体撮像デバイス1は、透明基板2と、透明基板2上にマトリクス状に配列された複数のDG−Tr3と、全てのDG−Tr3を被覆する保護絶縁膜4とを備える。DG−Tr3は、ボトムゲート電極21、半導体膜23、ドレイン電極27、ソース電極28及びトップゲート電極30等から構成されている。ライン41,42,43,44を介してボトムゲート電極21、ドレイン電極27、ソース電極28及びトップゲート電極30を導電配線50に接続し、導電配線50を電源101の陰極に接続し、固体撮像デバイス1を電解液102に浸漬し、電源101の陽極を電解液に浸漬する。そして、トップゲート電極30の透明性の変化を観察する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁層におけるコンタクトホールを形成した領域での膜残りを検出し、且つ層間絶縁層の膜残りの厚みを精度良く求める。

【解決手段】基板11に半導体層13及び半導体層13よりも酸化され難い第1検査用金属層27を形成し、半導体層13及び第1検査用金属層27を覆うように絶縁膜20を形成した後、絶縁膜20に半導体層13及び第1検査用金属層27をそれぞれ一部露出させるためのコンタクトホール21a及び検査用コンタクトホール21bを形成することで層間絶縁層21を形成し、層間絶縁層21にコンタクトホール21a及び検査用コンタクトホール21bの内部から表面にそれぞれ引き出された金属層22及び第2検査用金属層28を形成し、第1検査用金属層27と第2検査用金属層28との間の電気的特性を測定する。

(もっと読む)

導電性構造部、特に薄膜トランジスタ型液晶ディスプレイの非接触式コンタクト形成のための装置及び方法

【課題】導電性構造部が従来のようにまだ機械的にコンタクト形成のできない基板のもとでも検査の実施が可能となるように改善すること。

【解決手段】電界が導電性構造部(3)の機械的接触なしでの励起によって形成されるように構成する。

(もっと読む)

MIS型素子の評価方法、MIS型素子の評価用素子

【課題】複数のテスト素子によりMIS型素子の経時変化を評価可能であり、各々のテスト素子に位置依存性が少なく、印加電圧のばらつきも生じ難い、信頼性の高いMIS型素子の評価方法を提供する。

【解決手段】本発明のMIS型素子の評価方法は、MIS型素子95の層構造と同層にて、金属層265と半導体層267との間に絶縁層266が形成されてなるテスト素子201a〜201eを複数形成し、金属層265と半導体層267とを電極として複数のテスト素子201a〜201eをそれぞれ並列に接続して、各テスト素子201a〜201eに電圧印加した後、所定時間の経過後にテスト素子201aをサンプリングして当該テスト素子201aを評価する一方、さらに所定時間の経過後にテスト素子201bをサンプリングして当該テスト素子201bを評価する評価工程を順次行うことを特徴とする。

(もっと読む)

半導体薄膜の形成方法および半導体薄膜の検査装置

【課題】レーザアニールによる結晶化を利用した半導体薄膜の形成において、その結晶化度を従来よりも高精度に評価することが可能な半導体薄膜の形成方法を提供する。

【解決手段】p−Si膜23の結晶化度の検査処理の際に、p−Si膜23およびa−Si膜230へ向けて、LED12によって照射光Loutをそれぞれ照射する。これにより、p−Si膜23およびa−Si膜230の透過画像(透過画像データD1)を取得する。また、画像処理用コンピュータ15において、p−Si膜23(結晶化領域51)の透過輝度とa−Si膜230(未結晶化領域50)の透過輝度との透過コントラストを求める。そして求めた透過コントラストに基づいて、p−Si膜23に対する選別を行う。これにより、従来よりも確実な選別が実現される。

(もっと読む)

導電性組成物

【課題】導電性が十分に向上した導電性組成物を提供すること。

【解決手段】

導電性共役高分子と芳香族イミド化合物とを含む導電性組成物であって、導電性共役高分子が、芳香族イミド化合物とスタッキング安定構造を形成可能な高分子であり、且つ、スタッキング安定構造における、導電性共役高分子のHOMOと芳香族イミド化合物のLUMOとのHOMO−LUMO間重なり積分の絶対値が、0.008〜1.0となる部分を有する高分子である、導電性組成物。

(もっと読む)

41 - 60 / 180

[ Back to top ]