Fターム[5F110BB01]の内容

Fターム[5F110BB01]の下位に属するFターム

周辺回路と一体に形成されたもの (2,174)

Fターム[5F110BB01]に分類される特許

61 - 80 / 5,189

駆動用回路基板およびその製造方法並びに表示装置および電子機器

【課題】工程数が少なく、且つ、材料の利用効率が向上した駆動用回路基板およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本開示の表示装置は、一対のソース・ドレイン電極と、チャネル領域を形成すると共に、ソース・ドレイン電極に接して設けられた有機半導体層と、ソース・ドレイン電極まで貫通する貫通孔を有すると共に、有機半導体層およびソース・ドレイン電極上に設けられた少なくとも1層からなる絶縁層と、チャネル領域に対応する位置に設けられたゲート電極と、貫通孔を介して前記ソース・ドレイン電極に電気的に接続されると共に、ゲート電極と同一材料、且つ、同一膜厚で絶縁層上に設けられた画素用電極とを備える。

(もっと読む)

非対称ジベンゾジチエノチオフェン化合物

【課題】高い移動度と、優れた安定性を示す電子機器(例えば、薄膜トランジスタ)のための半導体層に使用できる半導体化合物および該化合物を使用した電子機器の提供。

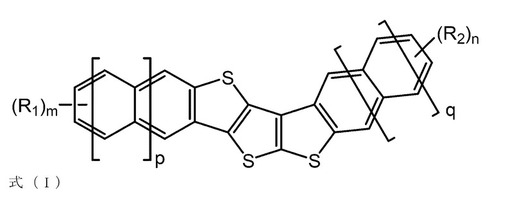

【解決手段】下記一般式(I)で表される非対称半導体化合物。

(式中、R1およびR2は、それぞれ独立してアルキル、置換アルキル、アルケニル等で、pおよびqは、独立して0または1である。)

(もっと読む)

ジオキサアンタントレン系化合物及び電子デバイス

【課題】高温雰囲気下にあっても特性に変化が生じ難い有機半導体材料(具体的には、ジオキサアンタントレン系化合物)を提供する。

【解決手段】本開示のジオキサアンタントレン系化合物は、以下の構造式(1)で表される。

ここで、Rは、炭素数が4以上の分岐を有するアルキル基である。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

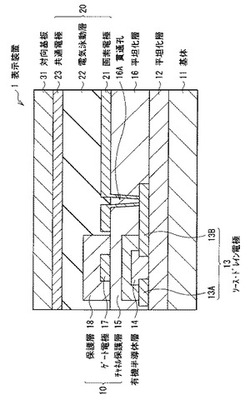

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置

【課題】アライメント精度良く半導体層を形成し、かつ、プロセス数を増やすことなくトランジスタの素子分離を行うことのできる薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置を提供する。

【解決手段】薄膜トランジスタ50は、基板1と、基板1上に形成されたゲート電極2と、基板1とゲート電極2とにわたって、これらの上に形成されたゲート絶縁体層4と、ゲート絶縁体層4上に形成された半導体層5と、半導体層5上に形成された保護層6と、ゲート絶縁体層4と半導体層5と保護層6とにわたって、これらの上に形成された、ソース電極7及びドレイン電極8と、を有し、半導体層5における、ソース電極7とドレイン電極8との間のチャネル部を流れる電流の方向の一端5aは、ソース電極7の一端7aと一致し、半導体層5における他端5bは、ドレイン電極8の一端8aと一致している。

(もっと読む)

表示装置の製造方法

【課題】輝度むらを低減することが可能な表示装置の製造方法を提供する。

【解決手段】基板に、酸化物半導体層を有する薄膜トランジスタを形成する工程と、前記薄膜トランジスタの上層に複数の表示素子よりなる表示領域を形成する工程とを含み、前記酸化物半導体層を形成する工程を、複数の分割部を平面状に継ぎ合わせた酸化物半導体よりなるターゲットと前記基板とを対面させて、スパッタリング法により行い、前記ターゲットの互いに平行な二本の継ぎ目の間隔を、前記継ぎ目に直交する方向において前記表示領域に生じる輝度分布の幅以下とする表示装置の製造方法。

(もっと読む)

半導体装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

高分子化合物及びそれを用いた電子素子

【課題】光電変換素子に含まれる有機層に用いた場合に、開放端電圧が大きくなる高分子化合物の提供。

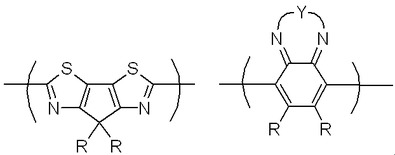

【解決手段】式(I)で表される構成単位、及び、式(II)で表わされる構成単位を有する高分子化合物。

(I)(II)〔式(I)及び式(II)中、Rは、水素原子、ハロゲン原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、アリールオキシ基、アリールチオ基、アリールアルキル基、アリールアルコキシ基、アリールアルキルチオ基、アシル基、アシルオキシ基、アミド基、酸イミド基、イミノ基、アミノ基、置換アミノ基、置換シリル基、置換シリルオキシ基、置換シリルチオ基、置換シリルアミノ基、複素環基、複素環オキシ基、複素環チオ基、アリールアルケニル基、カルボキシル基又はシアノ基を表す。Yは、2価の基を表す。〕

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体素子

【課題】酸化物半導体層を用いた半導体素子であって、Vthの変化が抑制された、特性の安定化した半導体素子を提供する。

【解決手段】In(インジウム)およびO(酸素)を含む酸化物半導体層と、Si(珪素)、F(フッ素)およびN(窒素)を含む絶縁層と、を有する半導体素子である。

(もっと読む)

シフトレジスタ回路

【課題】トランジスタのしきい値電圧の制御を行いながら、ゲート電極の電位は変動させず、バックゲート電極の電位のみを変動させることで、入力信号に応じた信号を出力することが可能な論理回路を有するシフトレジスタ回路を提供する。

【解決手段】同じ導電型の第1のトランジスタ及び第2のトランジスタを有する論理回路、を含むシフトレジスタ回路において、第1のトランジスタの第1のゲート電極を、第1のトランジスタのソース電極またはドレイン電極に接続し、第1のトランジスタの第2のゲート電極に入力信号を供給し、第2のトランジスタのゲート電極にクロック信号を供給し、第1のゲート電極と、ゲート電極とは、同じ層とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

薄膜トランジスタアレイ基板の製造方法

【課題】 有機樹脂膜を有するTFTアレイ基板の製造工程において、ブラシ洗浄の際に異物が有機平坦化膜表面にキズを生じさせることがある。このようにキズが生じた有機平坦化膜上に、画素電極となる透明電極膜を成膜した場合、キズ上の透明電極膜も断線してしまい、画素電極に信号が伝わらず表示不良を引き起こすことがある。

【解決手段】 有機平坦化膜を塗布する工程と、中間調露光を用いて有機平坦化膜に凹凸を形成する工程と、凹凸が形成された有機平坦化膜表面をロールブラシを用いて洗浄する工程と、洗浄工程後に、有機平坦化膜上に画素電極を構成する透明導電膜を成膜する工程とを備えた薄膜トランジスタアレイ基板の製造方法を提供する。

(もっと読む)

半導体装置、および半導体装置の作製方法

【課題】水分による電気特性劣化が抑制された半導体装置および半導体装置の作製方法を提供する。

【解決手段】トランジスタを覆う層間絶縁層に接して金属酸化物層が位置する構造とし、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層と、多結晶構造を有する第2の金属酸化物層を含む積層構造とする。アモルファス構造を有する第1の金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため格子間に水分をトラップしやすい。多結晶構造を有する第2の金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い。このため、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層が層間絶縁層に接する構造とすることにより、トランジスタ中への水分の侵入を効果的に防止できる。

(もっと読む)

表示装置

【課題】高開口率を有し、容量の大きな保持容量を有する表示装置を提供する。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

電気光学装置、電気光学装置の製造方法、及び電子機器

【課題】表示品質を向上させることが可能な電気光学装置、電気光学装置の製造方法、及び電子機器を提供する。

【解決手段】液晶装置100は、TFT30と、TFT30に電気的に接続された容量素子16とを備え、容量素子16は、TFT30と第2層間絶縁層11cを介して形成された第1容量電極16aと、第1容量電極16aに第1誘電体層16bを介して対向配置され、TFT30の半導体層30aに第2層間絶縁層11cに形成されたコンタクトホールCNT53を介して電気的に接続された第2容量電極16cとを有し、第2容量電極16cは、第1導電層16c1と第1導電層16c1上に積層された第2導電層16c2を有し、第1導電層16c1は、コンタクトホールCNT53と重なる領域が除去されてなり、第2導電層16c2と半導体層30aとがコンタクトホールCNT53を介して電気的に接続される。

(もっと読む)

61 - 80 / 5,189

[ Back to top ]