Fターム[5F110BB01]の内容

Fターム[5F110BB01]の下位に属するFターム

周辺回路と一体に形成されたもの (2,174)

Fターム[5F110BB01]に分類される特許

81 - 100 / 5,189

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

薄膜トランジスタならびに表示装置および電子機器

【課題】酸化物半導体層へ酸素を効率よく供給し、トランジスタ特性を向上することが可能な薄膜トランジスタおよびこれを備えた表示装置および電子機器を提供する。

【解決手段】本技術の薄膜トランジスタは、基板上に設けられたゲート電極と、ゲート電極に対応する位置にチャネル領域を有する酸化物半導体層と、チャネル領域を覆うチャネル保護膜と、チャネル保護膜の両側の酸化物半導体層上に設けられたソース電極およびドレイン電極と、少なくともソース電極およびドレイン電極上に設けられた保護膜と、酸化物半導体層に設けられ、保護膜と同一の構成材料が充填された1または2以上の凹部とを備える。

(もっと読む)

液晶表示装置及びその不良画素修復方法

【課題】本発明は、液晶表示装置及びその不良画素の修復方法を提供する。

【解決手段】第1の絶縁基板と、第1の絶縁基板上に実質的に第1の方向に互いに平行するように配値されたゲート配線およびストレージ配線と、ゲートおよびストレージ配線と絶縁されて交差し、実質的に第2の方向に配値されたデータ配線と、データ配線上に形成された保護膜と、保護膜上に形成された第1の画素電極と第2の画素電極と、第1の画素電極に隣接する第2の画素電極を含み、ストレージ配線は、実質的に第1の方向に配値された水平部および水平部から実質的に第2の方向に分枝し、データ配線とオーバーラップする垂直部を含み、垂直部は、第1の画素電極および第2の画素電極とオーバーラップし、第1の画素電極と垂直部がオーバーラップする幅は第2の画素電極および垂直部の間のオーバーラップする幅と実質的に同一であることを特徴とする液晶表示装置。

(もっと読む)

発光装置

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

酸化物半導体電界効果型トランジスタ及びその製造方法

【課題】移動度が高く、S値の低い電界効果型トランジスタの提供を目的とする。また、低温又は短時間の熱履歴でも高い特性の得られる電界効果型トランジスタの製造方法の提供を目的とする。

【解決手段】In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

(もっと読む)

電磁波剥離性フレキシブルデバイス用基板およびそれを用いた電子素子の製造方法

【課題】本発明は、安定的に電子素子部を形成可能な電磁波剥離性フレキシブルデバイス用基板を提供することを主目的とする。

【解決手段】本発明は、可撓性を有する金属基材と、上記金属基材の少なくとも一方の表面上に形成された絶縁層と、上記金属基材の他方の表面上に形成され、電磁波剥離性を有する電磁波剥離性粘着樹脂を含む電磁波剥離性粘着層と、を有することを特徴とする電磁波剥離性フレキシブルデバイス用基板を提供することにより、上記目的を達成する。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、並びに電気泳動ディスプレイ

【課題】画素電極間の距離が大きくて印刷に適し、しかも画素電極間の距離が大きい場合でも所望の表示を行うことができること。

【解決手段】薄膜トランジスタアレイは、絶縁基板1上に、少なくともゲート電極2と、ゲート絶縁膜3と、ソース電極4と、ドレイン電極5と、前記ドレイン電極5に接続された画素電極9と、ソース電極4とドレイン電極5との間に形成された半導体層6と、を有する薄膜トランジスタを、複数のゲート電極2がゲート配線2aに接続され、複数のソース電極4がソース配線4aに接続された状態でマトリクス状に配置した薄膜トランジスタアレイであって、隣り合う画素電極9の間の部分を線とし、複数の前記線が交わる部分を節として表したときに、画素電極9の配置が、1つの前記節に3本の前記線がつながる配置となる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁性基板に含まれている不純物が半導体層に作用するのを防止して、半導体装置の信頼性を向上させる。

【解決手段】

提供される半導体装置は、絶縁性基板1上に下地絶縁層2を介して半導体層3を形成する半導体装置に係り、下地絶縁層2に不純物として含まれるボロン又はアルミニウムの濃度が、絶縁性基板表面で1×1022原子/cm3以下で、かつ、絶縁性基板表面から100nm以上離れた領域で1×1019原子/cm3以下の条件を満たして、絶縁性基板表面から半導体層3に向かって漸次減少する態様で分布する。

(もっと読む)

表示装置

【課題】発光素子の劣化を極力抑えるための構造を提供すると共に、各画素に必要とされ

る容量素子(コンデンサ)を十分に確保するための構造を提供する。

【解決手段】トランジスタ上に、第1パッシベーション膜、第2の金属層、平坦化膜、バ

リア膜及び第3の金属層の順に積層され、平坦化膜に設けられた第1開口部の側面がバリ

ア膜に覆われ、第1開口部の内側に第2開口部を有し、かつ、第3の金属層は前記第1開

口部及び第2開口部を介して前記半導体に接続され、トランジスタの半導体、ゲート絶縁

膜、ゲート電極、第1パッシベーション膜及び前記第2の金属層で積層形成された容量素

子を備えたことを特徴とする。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】酸化物半導体を用いた低温プロセスで形成する信頼性の高い薄膜トランジスタ、その製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板100と、前記基板上の一部に設けられたゲート電極110と、前記ゲート電極を覆う第1の絶縁膜120と、前記第1の絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜130と、前記酸化物半導体膜上の一部に設けられた第2の絶縁膜150と、前記酸化物半導体膜から露出する酸化物半導体膜の一部と接続されたソース電極140Sおよびドレイン電極140Dと、を備え、前記酸化物半導体膜はInと、Gaと、Znのうち少なくとも一つの元素を含む酸化物半導体を有し、前記第1の絶縁膜中に含有される水素濃度が5×1020atm/cm−3以上であり、かつ、前記第2の絶縁膜中に含有される水素濃度が1019atm/cm−3以下である。

(もっと読む)

薄膜トランジスタアレイ、薄膜トランジスタアレイの製造方法、画像表示装置

【課題】高開口率を得るために形成する層間絶縁膜のパターニング性、歩留まりを向上させ、生産性に優れた薄膜トランジスタアレイを提供する。

【解決手段】ゲート絶縁膜2上には、ゲート電極11に重なる位置に、ドレイン電極16と、ソース電極17と、を隔てて設けてあり、ドレイン電極16には、画素電極15を接続し、ソース電極17には、ソース配線18を接続してある。また、ゲート絶縁膜2上には、ドレイン電極16及びソース電極17の双方に重なるように、半導体層3を設けてある。ゲート絶縁膜2上には、画素電極15の一部を露出させた状態で、ソース電極17、ソース配線18、ドレイン電極16、画素電極15、半導体層3を封止する一層目封止層4を設け、一層目封止層4上には、ソース電極17及びソース配線18に重なる位置に、二層目封止層5を設けてある。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、製造工程を単純化して透明導電膜上に金属膜が積層された積層構造を有する共通電極配線を製造することができる液晶表示装置の製造方法を提供する。

【解決手段】液晶表示装置の製造方法であって、透明導電膜10上に金属膜11が積層された積層構造を有する枠状の共通電極配線12と、透明導電膜10の配線幅よりも小さい配線幅を有する共通電極13と、共通電極配線12の透明導電膜10の配線幅よりも小さい配線幅を有する画素電極14とからなる横電界方式において、感光性樹脂膜15をエッチングマスクにして等方性エッチングにより、共通電極13および画素電極14となる透明導電膜10上に積層された、感光性樹脂膜15の下側に位置する金属膜11を除去するとともに、共通電極配線12となる透明導電膜上10に積層された、感光性樹脂15の下側に位置する金属膜11の側面の一部を除去する工程を含む。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

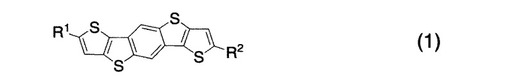

ジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタ

【課題】溶媒への溶解性に優れ、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体99〜80重量%及び特定式で示されるジチエノベンゾジチオフェン誘導体1〜20重量%からなることを特徴とするジチエノベンゾジチオフェン誘導体組成物。

(ここで、置換基R1及びR2は、同一又は異なって、n−ペンチル基、n−ヘキシル基、n−ヘプチル基及びn−オクチル基からなる群より選択される置換基を示す。)

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

表示装置及び表示装置の作製方法

【課題】TFTの特性ばらつきに起因する、画素間における発光素子の輝度のばらつきを低減し、信頼性が高く、画質の優れた表示装置を提供することを目的とする。

【解決手段】発光素子に接続するTFTを複数個、少なくとも2つ設け、それぞれのTFTの活性層を形成する半導体領域の結晶性を異ならせるものである。

当該半導体領域は、非晶質半導体膜をレーザーアニールにより結晶化させたものが適用されるが、結晶性を異ならせるために、連続発振レーザービームの走査方向を変えて、結晶成長の方向を互いに異ならせる方法を適用する。或いは、連続発振レーザービームの走査方向は同じとしても、個々の半導体領域間でTFTのチャネル長方向を変えて、結晶の成長方向と電流の流れる方向を異ならせる方法を適用する。

(もっと読む)

81 - 100 / 5,189

[ Back to top ]