Fターム[5F110BB08]の内容

Fターム[5F110BB08]に分類される特許

401 - 412 / 412

半導体装置、その製造方法及び電子機器

【課題】 スイッチングトランジスタ領域のSi−H結合が安定し、誘電体キャパシタ領域の強誘電体酸化膜に酸素欠損が発生しない半導体装置、その製造方法及びそれを使用した電子機器を提供する。

【解決手段】 ガラス等の基板1上に形成されたポリシリコン薄膜にソースドレイン拡散層4とチャネル領域3が形成され、更に、ゲート絶縁膜5を介してゲート電極6が形成されている。そして、層間絶縁膜8上に水素化窒化シリコン膜11が形成されており、これにより、スイッチング用薄膜トランジスタ7を含む能動素子領域の水素濃度を高く保つことができ、シリコン薄膜におけるSi−H結合が安定する。また、水素化窒化シリコン膜11の上に導電性酸化膜により形成された下部電極12を介して強誘電体膜13を設けることにより、強誘電体容量素子層の酸素濃度を高く保つことができ、強誘電体膜13における酸素欠損の発生を防止できる。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

ナノ構造単層の形成方法および形成デバイスならびにかかる単層を含むデバイス

ナノ構造配列の形成またはパターニング法が提供される。この方法は、ナノ構造会合基を含んでなるコーティング上での配列形成、レジストを使用するパターニングおよび/または配列形成を促進するデバイスの使用を含む。またナノ構造配列を含むデバイス(例えばメモリーデバイス)のように、ナノ構造配列の形成のための関連デバイスも提供される。 (もっと読む)

多機能ドープ導電性ポリマー系電界効果デバイス

電界駆動デバイス及び作動方法が提供される。各デバイスは、印加電界に対して多機能の応答を提供するために、一種以上のドープ導電性ポリマーを使用している。デバイスは、デバイス(10)用のゲートコンタクト(22)を提供するように作動できる導電層(30)と、デバイス(10)用のソース(24)及びドレイン(26)コンタクト並びに活性層を提供するように作動できる導電性ポリマー層(14)と、導電層(12)と導電性ポリマー層(14)との間に形成された絶縁性ポリマー層(16)とを有し、前記層の組合わせにより、複数の応答機能の内の少なくとも2機能を行うようにデバイス(10)が作動できる。 (もっと読む)

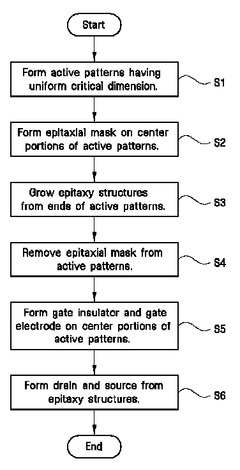

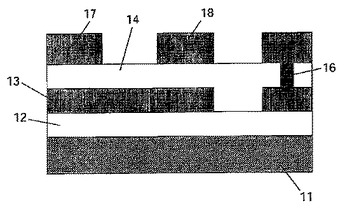

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

有機両極性半導体を使用する不揮発性強誘電体薄膜デバイス及びそのようなデバイスを処理するための方法

有機強誘電体高分子と有機両極性半導体との組み合わせを備える不揮発性強誘電体メモリデバイスが提案されている。本発明に係るデバイスは、高分子に適合し、また、高分子の利点、即ち、溶液処理、低コスト、低温層堆積及びフレキシブル基板との適合性を十分に活用している。  (もっと読む)

(もっと読む)

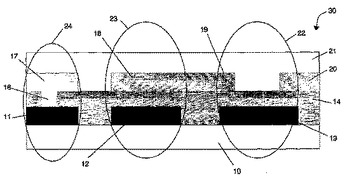

不揮発性強誘電体メモリ装置の製造方法及びその方法によって得られるメモリ装置

本発明は、トランジスタ22及びキャパシタ23を含んでいる不揮発性強誘電体メモリ装置30に関し、特に、不揮発性で、電気的に消去可能、かつプログラム可能な強誘電体メモリ素子及びそのような不揮発性強誘電体メモリ装置30を生産する方法に関する。本発明による方法は、トランジスタ22のゲート誘電体層及びキャパシタ23の誘電体層は同一の有機又は無機強誘電体層から作られるので、限られた数のマスクステップを含む。  (もっと読む)

(もっと読む)

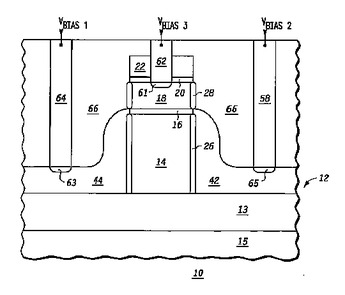

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

401 - 412 / 412

[ Back to top ]