Fターム[5F110CC01]の内容

Fターム[5F110CC01]の下位に属するFターム

順コプレナドープ (4,463)

Fターム[5F110CC01]に分類される特許

2,081 - 2,099 / 2,099

複合金属酸化物を含むチャネルを有する半導体デバイス

例示的な一実施形態には半導体デバイスが含まれる。当該半導体デバイスは、亜鉛−ガリウム、カドミウム−ガリウム、カドミウム−インジウムを含む金属酸化物のうちの1つ又は複数を含んで成るチャネルを具備し得る。 (もっと読む)

二元酸化物の混合物を含むチャネルを有する半導体デバイス

半導体デバイスは、第1の二元酸化物及び第2の二元酸化物を含むチャネルを備えることができ、第2の二元酸化物はCdO、SrO、CaO又はMgOから選択される。 (もっと読む)

高分子酸コロイドを用いて生成した電子用途向け水分散性ポリピロール

少なくとも1種のポリピロールおよび少なくとも1種のコロイド形成性高分子酸の水性分散液を含む組成物が、このような組成物の製造方法で得られる。新規な組成物は、有機発光ダイオードディスプレイなどの有機電子デバイス、メモリ記憶装置、電磁遮蔽、エレクトロクロミックディスプレイ、薄膜トランジスタ、電界効果抵抗デバイスをはじめとする電子デバイスにおいて有用である。  (もっと読む)

(もっと読む)

ドープされた部分を有する堆積チャネル領域を含むトランジスタ

ゲート電極(12、60)と、ソース電極(20、62)と、ドレイン電極(22、64)と、誘電体材料(16、70)と、ソース電極(20、62)とドレイン電極(22、64)との間に配置されるチャネル領域(18、80)とを有するトランジスタ(10、40、42、44、46)。チャネル領域(18、80)が、不純物がドープされている部分(82)を含み、これにより、チャネル領域(18、80)の残りの部分に対して、その部分(82)内の固定電荷密度が変えられる。  (もっと読む)

(もっと読む)

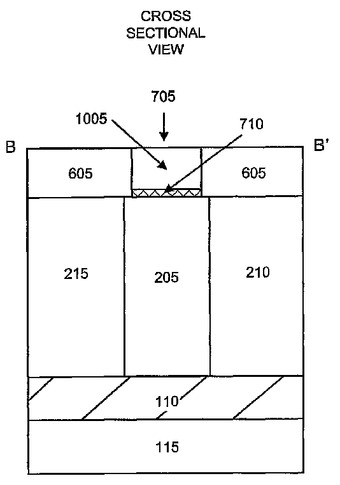

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

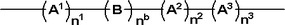

有機半導体材料、有機トランジスタ、電界効果トランジスタ、スイッチング素子及びチアゾール化合物

下記一般式で表される部分構造を持つ化合物を含有することを特徴とする有機半導体材料、それを用いた有機トランジスタ及び電界効果トランジスタ、及び該有機トランジスタまたは該電界効果トランジスタを用いるスイッチング素子。

(式中、Bはチアゾール環をもつユニットを表し、A1,A2はそれぞれ独立にアルキルを置換基として持つユニットを表し、A3は二価の連結基を表し、nbは1〜20の整数を表し、n1、n2はそれぞれ独立に0〜20の整数を表し、n3は0〜10の整数を表す。)

(もっと読む)

歪みFINFETチャネルの製造方法

例示的実施形態はFinFETチャネル構造の形成法に関する。当該方法において、絶縁層(130)上に化合物半導体層(140)を提供し、化合物半導体層(140)上にトレンチ(142)を提供し、かつ、化合物半導体層(140)上およびトレンチ(142)内に歪み半導体層(144)を提供する。該方法において、さらに、化合物半導体層(140)上から歪み半導体層(144)を除去し、その結果、トレンチ(142)内に歪み半導体層(144)を残し、化合物半導体層(140)を除去して、歪み半導体層(144)を残し、かつ、フィン形のチャネル領域(152)を形成する。  (もっと読む)

(もっと読む)

両極性発光電界効果トランジスタ

トランジスタのチャネル長を規定する長さLによって分離される電子注入電極及び正孔注入電極と接触する有機半導体層を備え、発光元の有機半導体層の領域は、電子注入電極及び正孔注入電極の両方からL/10より離れている両極性発光トランジスタ。  (もっと読む)

(もっと読む)

N−チャネルトランジスタ

電子親和力がEAsemicondである有機半導体層と、前記半導体層と界面を形成する有機ゲート誘電体層とを備えるn−チャネルまたは両極性の電界効果トランジスタであって、前記ゲート誘電体層中のトラッピング基のバルク濃度が1018cm−3未満であり、この場合、トラッピング基は(i)EAsemicond以上の電子親和力EAxおよび/または(ii)(EAsemicond−2eV)以上の反応性電子親和力EArxnを持つ基であることを特徴とする、n−チャネルまたは両極性の電界効果トランジスタである。  (もっと読む)

(もっと読む)

有機薄膜トランジスタの製造方法及び該製造方法により作製される有機薄膜トランジスタとそのシート

熱可塑性半導体材料を含む層及び、該層に接合する金属微粒子を含む層を形成して、押圧後加熱するか押圧と加熱を同時に行い、半導体層、ソース電極、ドレイン電極とする有機薄膜トランジスタの製造方法、および、支持体シート上に、ゲートバスライン及びソースバスラインを介して連結された複数の有機薄膜トランジスタが形成され、該薄膜トランジスタのソース電極及びドレイン電極が、当該電極を構成する金属相の少なくとも1部が熱可塑性半導体材料を含む半導体層に混入して、該半導体層に接合することを特徴とする有機薄膜トランジスタシート。 (もっと読む)

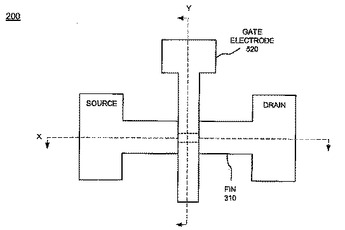

セルフアラインされたダマシンゲート

基板上のフィン領域、ソース領域、およびドレイン領域をパターン化するステップと、フィン領域中にフィン(310)を形成するステップと、フィン領域中にマスク(320)を形成するステップと、を含む、MOS電界効果トランジスタ(MOSFET)(200)を形成する方法である。この方法は、MOSFETのチャネル領域(330)を露出するように、マスク(320)をエッチングするステップと、チャネル領域(330)中のフィン(310)の幅を薄くするようにフィン(310)をエッチングするステップと、フィン(310)上にゲートを形成するステップと、ゲート、ソース領域およびドレイン領域に対するコンタクトを形成するステップと、をさらに含む。  (もっと読む)

(もっと読む)

薄膜トランジスタ及びその製造方法

本発明の薄膜トランジスタは、半導体層(14)と、前記半導体層に相互に対向するように分離して設けられたソース領域(15)とドレーン領域(16)とを有する薄膜トランジスタ(100)であって、前記半導体層はπ共役系有機半導体分子を主成分として有し、前記π共役系有機半導体分子が、π軌道が実質的に対向するように配向され、かつ主鎖の分子軸が前記半導体層に形成されるチャネルにおける電界の方向に対して傾斜して配向されている。 (もっと読む)

二重ゲートトランジスタ半導体製造プロセス用の限定スペーサ

半導体製造プロセスは、基板上にシリコンフィンを形成することを含む。フィンの主面上にはゲート誘電体が形成される。フィンの少なくとも2つの面の上にゲート電極が形成される。次いで、ゲート電極の側壁に近接して誘電体スペーサが選択的に形成されて、誘電体スペーサが該側壁に限定されることによって、主フィン面の大部分が露出したままとされる。その後、主フィン面上にシリサイドが形成される。一実施形態では、ゲート電極の形成は、フィンおよび基板の上にポリシリコンを堆積し、ポリシリコンの上にキャッピング層を堆積し、キャッピング層の上にフォトレジストをパターニングし、パターニングしたフォトレジストが適所に配された状態でキャッピング層およびポリシリコンをエッチングすることを含む。エッチングによりポリシリコンの幅はキャッピング層の幅よりも小さくなり、ポリシリコンの側壁に隣接するキャッピング層の下に空隙ができ、ここに限定スペーサを形成することができる。  (もっと読む)

(もっと読む)

弱く結合した層からなる無機半導体を用いた電界効果トランジスタ

電界効果トランジスタは、ソース電極と、ドレイン電極と、ゲート電極と、無機半導体の結晶または多結晶の層と、誘電体層とを含む。無機半導体の層は、物理的にソース電極からドレイン電極まで延びる活性チャネル部分を有する。無機半導体は、層内の結合力が共有結合および/またはイオン結合である2次元の層の積み重ねを有する。互いに隣接する層のそれぞれが、共有結合およびイオン結合の力よりかなり弱い力によって互いに結合される。誘電体層は、ゲート電極と無機半導体材料の層の間に介在する。ゲート電極は、無機半導体の層の活性チャネル部分の導電率を制御するように構成される。

(もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

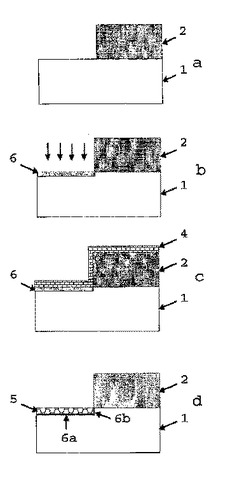

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

金属電極を備えているトランジスタデバイスおよびそのようなデバイスを形成する際に用いるための方法

金属ソース電極と、金属ドレイン電極と、金属ゲート電極と、堆積させた半導体材料内のチャネルとを有するトランジスタデバイスであって、金属ゲート電極、金属ソース電極の第1の金属部分、および金属ドレイン電極の第1の金属部分を含む第1の層と、金属ソース電極の第2の金属部分、金属ドレイン電極の第2の金属部分、堆積させた半導体材料、および半導体材料と金属ゲート電極との間にある誘電体材料を含む第2の層と、基板を含む第3の層とを含み、第1の層、第2の層および第3の層は、第2の層が第1の層と第3の層との間に配置されるような順序で構成されているトランジスタデバイス。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

2,081 - 2,099 / 2,099

[ Back to top ]