Fターム[5F110EE15]の内容

Fターム[5F110EE15]に分類される特許

81 - 100 / 1,118

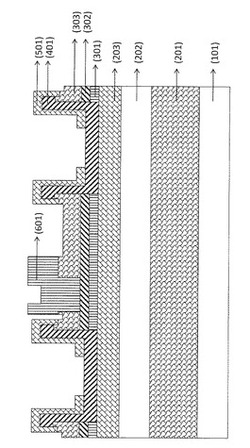

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制できる半導体装置を提供する。

【解決手段】ボトムゲート電極12aとトップゲート電極17aで半導体層14を挟むデュアルゲート型の薄膜トランジスタを有する半導体装置において、前記トップゲート電極は、第1のブラックマトリックス層によって形成され、前記半導体層は、前記トップゲート電極によって覆われている半導体装置である。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なプログラマブルなアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルを複数並列に接続されたプログラマブル回路とし、ユニットセル毎に導通または非導通の切り替えを行う。また、当該ユニットセルのスイッチとして、オフ電流を十分に小さくすることができる第1のトランジスタと、ゲート電極が第1のトランジスタのソース電極又はドレイン電極と電気的に接続された第2のトランジスタと、を含む構成とし、当該第2のトランジスタのゲート電位によってユニットセルの導通または非導通を制御する。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

薄膜トランジスタ

【課題】高い電界効果移動度を有する薄膜トランジスタを提供する。

【解決手段】希ガス及び水分子を含有する混合気体雰囲気下で酸化物半導体材料を成膜してなるチャネル層を備える薄膜トランジスタであって、前記酸化物半導体材料がIn原子及びZn原子を含む酸化物であり、原子比Zn/(In+Zn)が10原子%以上20原子%未満である薄膜トランジスタ。

(もっと読む)

フォトセンサの駆動方法、半導体装置の駆動方法、半導体装置、及び電子機器

【課題】小型でコントラストの高い画像データを取得することができるフォトセンサを提供する。該フォトセンサを用いた半導体装置を提供する。

【解決手段】受光素子と、スイッチング素子であるトランジスタと、トランジスタを介して受光素子と電気的に接続する電荷保持ノードとを有するフォトセンサにおいて、導通状態から非導通状態とするためにトランジスタへ供給する駆動パルスの入力波形の立ち下がり時間を遅延させ、電荷保持ノードが保持する電荷の減少を抑制する。

(もっと読む)

半導体装置

【課題】フォトセンサを有する半導体装置において、外光のノイズを軽減し、且つトランジスタのオフ電流によるリークが原因となるノイズも低減する。

【解決手段】マトリクス状に配置された複数のフォトセンサを有する。複数のフォトセンサはそれぞれ、光電変換素子と増幅回路とを有する。バックライトを点灯して被検出物に光を照射して第p行目のフォトセンサでリセット動作及び蓄積動作を行った後、バックライトを非点灯として第(p+1)行目のフォトセンサでリセット動作及び蓄積動作を行い、その後全行のフォトセンサの選択動作を順次行う。隣接する行のフォトセンサで得られた出力信号の差分を取得し、差分を用いて被検出物の撮像画像の生成や被検出物の存在する領域の検出を行う。増幅回路は蓄積された電荷を保持するトランジスタを有し、当該トランジスタはチャネルが酸化物半導体層に形成される。

(もっと読む)

半導体装置

【課題】動作特性および信頼性の向上した、新規なマルチゲート構造のトランジスタを提

供することを課題とする。

【解決手段】2つ以上のゲート電極と、直列に接続した2つ以上のチャネル形成領域、ソ

ース領域、ドレイン領域、及び高濃度不純物領域を有する半導体層と、を有するマルチゲ

ート構造のトランジスタにおいて、ソース領域側に近接するチャネル形成領域のチャネル

長が、ドレイン領域側に近接するチャネル形成領域のチャネル長よりも大きくする。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】非接触にて、被写体の位置情報の取得を容易に行うことができる固体撮像装置、または半導体表示装置の提供。

【解決手段】第1入射方向から第1入射角を有する光が入射する複数の第1フォトセンサと、第1入射方向とは異なる第2入射方向から第2入射角を有する光が入射する複数の第2フォトセンサとを有し、複数の第1フォトセンサのうち、第1入射方向の上流側の一つの第1フォトセンサの方が、第1入射方向の下流側の他の一つの第1フォトセンサよりも、第1入射角が大きく、複数の第2フォトセンサのうち、第2入射方向の上流側の一つの第2フォトセンサの方が、第2入射方向の下流側の他の一つの第2フォトセンサよりも、第2入射角が大きい。

(もっと読む)

半導体装置

【課題】電源をオフしてもデータを保持することができ、退避動作と復帰動作が不要なレジスタ回路を提供する。

【解決手段】複数のレジスタ構成回路と、オフ電流が小さい第1のトランジスタと、オフ電流が小さい第2のトランジスタと、を有するレジスタ回路において、データ保持部を前記第1のトランジスタのソース及びドレインの一方に接続し、前記第2のトランジスタのソース及びドレインの一方に接続する。前記第1のトランジスタ及び前記第2のトランジスタはオフ電流が小さいので、データ保持部の電荷がリークせず、レジスタ回路の電源をオフしてもデータ保持部にデータが保持される。そのため、退避動作と復帰動作を行わなくてよい。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

81 - 100 / 1,118

[ Back to top ]