Fターム[5F110EE15]の内容

Fターム[5F110EE15]に分類される特許

1,101 - 1,118 / 1,118

半導体装置および半導体装置の作製方法

(課題)

本発明は、被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、本発明は、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子(薄膜ダイオード、シリコンのPIN接合からなる光電変換素子やシリコン抵抗素子)を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)

基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化を行い金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。  (もっと読む)

(もっと読む)

液晶用マトリクス基板およびその製造方法

【課題】 表示品位が高く、周辺回路とのコンタクト性に優れた液晶表示装置を構成するマトリックス基板およびその製造方法を実現する。

【解決手段】 複数の液晶セルを形成するためのマトリクス回路が形成されている液晶用マトリクス基板において、液晶パネルを組み立てるときに貼り合わせ面となる表面に島状に、第1の導電材からなる絵素電極12と、第2の導電材からなる端子電極13とを形成する。このとき、第1の導電材は、第2の導電材よりも透過性が高く、かつ、導電性が低いものを使用する。

(もっと読む)

TFT−LCDの画素構造及びその製造方法

【課題】 4回のマスク工程によって形成されるTFT−LCDの画素構造及びその製造方法を提供する。

【解決手段】 基板の上に透明導電層と第1金属層を順に形成し、第1金属層と透明導電層をパターン化して、ゲートパターンと画素電極パターンを形成する。次に、ゲート絶縁層と半導体層を基板の上に形成し、パターン化工程によりゲートパターン上方にあるゲート絶縁層と半導体層を保留すると同時に、画素電極パターンの第1金属層を除去する。そして、基板の上に第2金属層を形成し、該第2金属層をパターン化し、半導体層上にソースパターンとドレインパターンを形成する。最後に、基板の上に保護層を形成し、該保護層をパターン化し、画素電極パターンの透明導電層を露出させる。

(もっと読む)

半導体装置、及びそれらの作製方法

【課題】 本発明では、工程、装置を複雑化することなく、要求される特性を有する薄膜トランジスタを作製することを目的とする。また、薄膜トランジスタの特性を精密に自由に制御することで、高い信頼性や優れた電気特性を有する半導体装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 本発明は、薄膜トランジスタにおいて、ゲート電極層で覆われている半導体層のソース領域側かドレイン領域側の一方に、低濃度不純物領域を作製する。低濃度不純物領域は、ゲート電極層をマスクとして、半導体層表面に対し、斜めにドーピングすることによって形成される。よって、薄膜トランジスタの微細な特性の制御を行うことができる。

(もっと読む)

半導体装置、及びそれらの作製方法

【課題】 本発明では、工程、装置を複雑化することなく、要求される特性を有する薄膜トランジスタを作製することを目的とする。また、薄膜トランジスタの特性を精密に自由に制御することで、高い信頼性や優れた電気特性を有する半導体装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 本発明は、薄膜トランジスタにおいて、ゲート電極層で覆われている半導体層のソース領域側かドレイン領域側の一方に、低濃度不純物領域を作製する。低濃度不純物領域は、ゲート電極層をマスクとして、半導体層表面に対し、斜めにドーピングすることによって形成される。よって、薄膜トランジスタの微細な特性の制御を行うことができる。

(もっと読む)

レーザ光を照射する方法及び装置、並びに非単結晶半導体膜をアニールする方法及び半導体装置を作製する方法

【課題】 レンズアレイを用いて結晶化等を行う際に照射体において反射した戻り光による悪影響を回避した、レーザ発振器の安定性を高く保ち、かつ均一なレーザ処理をすることができるレーザ照射技術、並びにそれを用いる結晶化方法及び半導体装置の作製方法の提供。

【解決手段】 レーザ発振器から射出されたレーザ光をシリンドリカルレンズアレイ等のレンズアレイを通過させて複数に分割し、分割後のレーザ光を焦点を結ぶ位置でスリットの開口を通過させ、その後更に集光レンズを通過させて照射面上に照射する。

このようにして、スリットを用いることにより照射体で反射した戻り光をカットし、レーザの出力又は周波数の変動や、ロッドの破壊を防ぐものであり、その結果レーザ光の出力を安定化させ、これによって、安定して強度分布の均一なレーザ光を照射面において照射することができ、均一なアニールを行う。

(もっと読む)

配線層の形成方法、配線層および薄膜トランジスタ

【課題】 配線膜厚が200〜1000nm程度のサブμmオーダの薄膜でも2.5μΩcm以下の比抵抗を得ること配線層の形成方法および配線層を提供すること。

【解決手段】 ガラス基板1上に下地絶縁膜2の窒化シリコン膜を形成し、この上に下地金属層3を形成し、この上に金属シード層4を形成し、この金属シード層4上に金属配線層7を形成した配線層であって、上記金属シード層4は主として結晶面が(111)に配向し、平均結晶粒径が0.25μm以上であり、上記金属配線層は膜厚が200乃至1000nmであり、無電解めっき法で形成された層である。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

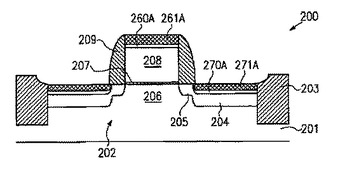

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

1,101 - 1,118 / 1,118

[ Back to top ]