Fターム[5F110FF03]の内容

Fターム[5F110FF03]に分類される特許

121 - 140 / 5,365

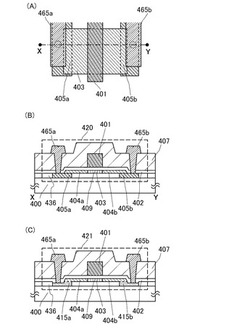

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置、発光装置、及び電子機器

【課題】動作不良を抑制する。

【解決手段】電界効果トランジスタと、スイッチと、容量素子と、を設ける。電界効果トランジスタは、チャネル形成領域を介して互いに重畳する第1のゲート及び第2のゲートを有し、第2のゲートの電位に応じて閾値電圧の値が変化する。スイッチは、電界効果トランジスタのソース及びドレインの一方と、電界効果トランジスタにおける第2のゲートと、を導通状態にするか否かを制御する機能を有する。容量素子は、電界効果トランジスタにおける第2のゲートと電界効果トランジスタにおけるソース及びドレインの他方との間の電圧を保持する機能を有する。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、製造工程を単純化して透明導電膜上に金属膜が積層された積層構造を有する共通電極配線を製造することができる液晶表示装置の製造方法を提供する。

【解決手段】液晶表示装置の製造方法であって、透明導電膜10上に金属膜11が積層された積層構造を有する枠状の共通電極配線12と、透明導電膜10の配線幅よりも小さい配線幅を有する共通電極13と、共通電極配線12の透明導電膜10の配線幅よりも小さい配線幅を有する画素電極14とからなる横電界方式において、感光性樹脂膜15をエッチングマスクにして等方性エッチングにより、共通電極13および画素電極14となる透明導電膜10上に積層された、感光性樹脂膜15の下側に位置する金属膜11を除去するとともに、共通電極配線12となる透明導電膜上10に積層された、感光性樹脂15の下側に位置する金属膜11の側面の一部を除去する工程を含む。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】酸化物半導体を用いた低温プロセスで形成する信頼性の高い薄膜トランジスタ、その製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板100と、前記基板上の一部に設けられたゲート電極110と、前記ゲート電極を覆う第1の絶縁膜120と、前記第1の絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜130と、前記酸化物半導体膜上の一部に設けられた第2の絶縁膜150と、前記酸化物半導体膜から露出する酸化物半導体膜の一部と接続されたソース電極140Sおよびドレイン電極140Dと、を備え、前記酸化物半導体膜はInと、Gaと、Znのうち少なくとも一つの元素を含む酸化物半導体を有し、前記第1の絶縁膜中に含有される水素濃度が5×1020atm/cm−3以上であり、かつ、前記第2の絶縁膜中に含有される水素濃度が1019atm/cm−3以下である。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

スパッタリングターゲット、トランジスタ、焼結体の製造方法、トランジスタの製造方法、電子部品または電気機器、液晶表示素子、有機ELディスプレイ用パネル、太陽電池、半導体素子および発光ダイオード素子

【課題】WS2を主成分とするスパッタリングターゲットを提供する。

【解決手段】本発明の一態様は、Hf,Re,Ta,W,Nb,Zr,V,Al,In,Sn,Ga,Zn,Si,Ge,Mn,Ni,Fe,Co,Cu,Ag,Y,Sc,Mg,Caからなる群から選ばれた少なくとも一種類以上の元素を合計で0.1〜10.0wt%含有し、残部がWS2および不可避的不純物からなることを特徴とするスパッタリングターゲットである。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

スイッチング素子及びその製造方法

【課題】CNTとゲート絶縁膜との相互作用を高め、良好かつ安定したトランジスタ特性を示すスイッチング素子を提供する。

【解決手段】本発明のスイッチング素子は、ゲート絶縁膜と、前記ゲート絶縁膜に接して形成された活性層とを具備する。前記活性層は、カーボンナノチューブを含み、前記ゲート絶縁膜は、側鎖に芳香族環を有する非共役高分子を含んでいる。

(もっと読む)

Cu−Mn合金スパッタリングターゲット材、それを用いた薄膜トランジスタ配線及び薄膜トランジスタ

【課題】高いバリア性を有するCu−Mn合金膜を形成する。

【解決手段】半導体素子の配線の形成に用いられるCu−Mn合金スパッタリングターゲット材10であって、濃度が8原子%以上30原子%以下のMnと、不可避的不純物とを含むCu−Mn合金からなり、Cu−Mn合金の平均結晶粒径が10μm以上50μm以下である。

(もっと読む)

酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板

【課題】理論的根拠に基づいて酸化物半導体の母材料に添加される物質を使用することによって、優れた特性を有する酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板を提供する。

【解決手段】 本発明の一実施形態に係る酸化物半導体は、亜鉛(Zn)及び錫(Sn)のうちの少なくとも一つの元素を含む第1物質、及び前記第1物質に添加される第2物質を含み、前記第1物質と酸素(O)との電気陰性度差値から前記第2物質と酸素(O)との電気陰性度差値を引いた値が1.3以下であることを特徴とする。

(もっと読む)

スパッタリングターゲット、トランジスタ、焼結体の製造方法、トランジスタの製造方法、電子部品または電気機器、液晶表示素子、有機ELディスプレイ用パネル、太陽電池、半導体素子および発光ダイオード素子

【課題】MoS2を主成分とするスパッタリングターゲットを提供する。

【解決手段】本発明の一態様は、Hf,Re,Ta,W,Nb,Zr,V,Al,In,Sn,Ga,Zn,Si,Ge,Mn,Ni,Fe,Co,Cu,Ag,Y,Sc,Mg,Caからなる群から選ばれた少なくとも一種類以上の元素を合計で0.1〜10.0wt%含有し、残部がMoS2および不可避的不純物からなることを特徴とするスパッタリングターゲットである。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】高い移動度を実現でき、且つ、ストレス耐性(ストレス印加前後のしきい値電圧シフト量が少ないこと)にも優れた薄膜トランジスタ用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、Zn、Sn、およびInと;Si、Hf、Ga、Al、Ni、Ge、Ta、W、およびNbよりなるX群から選択される少なくとも一種の元素(X群元素)と、を含むものである。

(もっと読む)

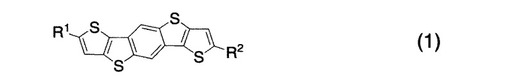

ジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタ

【課題】溶媒への溶解性に優れ、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体99〜80重量%及び特定式で示されるジチエノベンゾジチオフェン誘導体1〜20重量%からなることを特徴とするジチエノベンゾジチオフェン誘導体組成物。

(ここで、置換基R1及びR2は、同一又は異なって、n−ペンチル基、n−ヘキシル基、n−ヘプチル基及びn−オクチル基からなる群より選択される置換基を示す。)

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

121 - 140 / 5,365

[ Back to top ]