Fターム[5F110FF40]の内容

Fターム[5F110FF40]に分類される特許

1 - 20 / 34

表示装置

【課題】熱処理による特性変動を抑制した酸化物半導体を用いた表示装置を提供する。

【解決手段】実施形態によれば、絶縁層と、絶縁層上のゲート電極と、ゲート電極上にゲート絶縁膜を介して設けられ酸化物層より形成された半導体層と、半導体層の上において、ゲート電極を挟むように離間して設けられたソース電極及びドレイン電極と、を含む薄膜トランジスタと、ソース電極及びドレイン電極のいずれかに接続され、前記酸化物層より形成され前記半導体層よりも電気抵抗が低い画素電極と、画素電極に与えられる電気信号によって光学特性の変化と発光との少なくともいずれかを生ずる光学素子と、画素電極の下に設けられゲート絶縁膜と同じ材料で形成された膜と、を備え、ゲート電極の上のゲート絶縁膜の半導体層の側の表面は、画素電極の下に設けられた膜の画素電極の側の表面よりも平滑性が高い表示装置が提供される。

(もっと読む)

Ga2O3系半導体素子

【課題】高品質のGa2O3系半導体素子を提供する。

【解決手段】一実施の形態として、α−Al2O3基板2上に形成されたα−(AlxGa1−x)2O3単結晶(0≦x<1)からなるp型α−(AlxGa1−x)2O3単結晶膜3と、p型α−(AlxGa1−x)2O3単結晶膜3上に形成されたソース電極12及びドレイン電極13と、p型α−(AlxGa1−x)2O3単結晶膜3中に形成され、ソース電極12及びドレイン電極13にそれぞれ接続されたコンタクト領域14、15と、α−Al2O3基板2のp型α−(AlxGa1−x)2O3単結晶膜3と反対側の面上の、コンタクト領域14とコンタクト領域15との間に形成されたゲート電極11と、を含むGa2O3系FET10を提供する。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

電子素子及びその製造方法

【課題】素子性能の低下が抑制される電子素子を提供する。

【解決手段】基板12と、前記基板上の動作領域に配置された第1導電層14Gと、前記第1導電層上に該第1導電層と接して配置された絶縁層16と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂30の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部22と、を有する電子素子10。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】基板の反りを防止可能な構造を備えたことにより長期的な強度および特性の確保が可能な薄膜トランジスタ基板の製造方法を提供する。

【解決手段】基板3上に成膜されたゲート絶縁膜7と、ゲート絶縁膜7上にパターン形成された半導体薄膜9とを備えた薄膜トランジスタ基板1において、ゲート絶縁膜7における半導体薄膜9の外側となる位置には、溝パターン101が設けられている。ゲート絶縁膜7は、窒化シリコン膜7aとその上部の酸化シリコン膜7bとの積層構造からなり、溝パターン101は、窒化シリコン膜7aに形成されている。基板3はガラス材料からなる。

(もっと読む)

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】

転写型に形成された絶縁膜を基板上に形成された接着膜に転写する際、接着膜の膜厚の不均一を低減する薄膜トランジスタの製造方法を提供する。

【解決手段】

凹凸パターンが形成された転写型に半導体膜を形成する半導体膜形成ステップS11と、半導体膜が形成された転写型に絶縁膜を形成する絶縁膜形成ステップS12と、基板上に予め形成された電極上に接着膜を形成する接着膜形成ステップS02と、接着膜を硬化させる硬化ステップS03と、硬化した接着膜を介して電極上に絶縁膜および半導体膜を転写する転写ステップS21とを備える。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

電界効果型有機トランジスタ

【課題】ゲート絶縁層に含まれる高誘電体粒子がゲート電極側に偏在していない場合に比べ、低電圧でも駆動する電界効果型有機トランジスタを提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記チャネル層は有機半導体層であり、前記ゲート絶縁層は高誘電体粒子及び絶縁性樹脂を含み、前記高誘電体粒子がゲート電極側に偏在している電界効果型有機トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明の半導体装置は、良好なカットオフ特性と高速動作とを両立して改善できる。

【解決手段】 本発明の半導体装置は、基板と、基板上に形成され、バンドギャップが生成されたグラフェンを有するチャネル領域と、チャネル領域の両側に形成され、チャネル領域のグラフェンに比して小さいバンドギャップが生成されたグラフェンを有するソース/ドレイン領域と、ソース/ドレイン領域のチャネルに接する部分の上に、夫々形成された第1および第2のゲート電極と、を備えることを特徴とする。

(もっと読む)

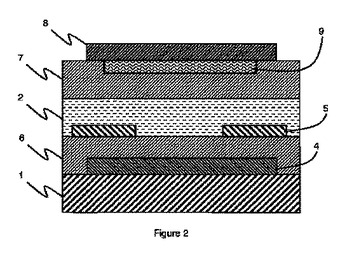

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

トンネル電界効果デバイス

【課題】 トンネル電界効果トランジスタ(TFET)構造用の間接誘導トンネル・エミッタを提供する。

【解決手段】 このTFET構造は、第1の半導体材料から形成された細長いコア・エレメントを少なくとも部分的に取り囲み、TFET構造のソース領域に対応する位置に配置された外装と、外装とコア・エレメントとの間に配置された絶縁体層と、外装をコア・エレメントにショートさせるソース接点とを含み、ON状態中にTFET構造のチャネル領域内にトンネリングするために十分なキャリア濃度をコア・エレメントのソース領域に導入するように外装が構成される。

(もっと読む)

半導体装置の作製方法

【課題】薄膜トランジスタのしきい値電圧を制御するため、薄膜トランジスタのチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設けた際に、プロセス数の増加を招くことなく、電気特性の優れた薄膜トランジスタを備えた半導体装置を得ることを課題の一つとする。

【解決手段】酸化物半導体層の上方に設けるゲート電極を形成するとき、酸化物半導体層のパターニングと同時に形成することで、第2のゲート電極の作製に要するプロセス数の増加を削減する。

(もっと読む)

薄膜トランジスタおよびアクティブマトリクスディスプレイ

【課題】ボトムゲート型の薄膜トランジスタにおいて、オンオフ比の高いトランジスタを提供すること。

【解決手段】絶縁基板101上に少なくともゲート電極102と、ゲート絶縁層103が順次積層され、このゲート絶縁層上に酸化物を含む半導体層104とソース電極105およびドレイン電極106が設けられたボトムゲート型の薄膜トランジスタであって、半導体層のゲート側の面の酸素密度が、反対の面の酸素密度よりも低いことを特徴とする薄膜トランジスタとする。このため半導体層104に酸素含有プラズマを照射する。

(もっと読む)

半導体装置

【課題】動作性能および信頼性の高い半導体装置の提供を課題とする。

【解決手段】シリコン基板上に設けられた酸化シリコン膜と、単結晶シリコン基板の一部よりなりTFTの活性層となる単結晶の島状シリコン層となる前の単結晶シリコン基板を熱酸化して得られ、酸化シリコン膜に貼り合わせ界面にて貼り合わせて設けられた膜厚が0.05μm〜0.5μmの酸化シリコン膜と、活性層を熱酸化して設けられた他の面の酸化シリコン膜と、により取り囲まれた活性層と、活性層上に設けられたゲート電極と、を有し、単結晶の島状シリコン層は、膜厚が0.05μm〜0.5μmの酸化シリコン膜を介して水素が導入された単結晶シリコン基板を水素が導入された部分で分断して得られたものである半導体装置を提供する。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】有機電界発光表示装置及びその製造方法を提供する。

【解決手段】画素領域と非画素領域を備える基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置し、チャネル領域及びソース/ドレイン領域を備える半導体層と、前記半導体層のチャネル領域に対応するように位置するゲート電極と、前記半導体層と前記ゲート電極とを絶縁させるゲート絶縁膜と、前記半導体層のソース/ドレイン領域に電気的に接続するソース/ドレイン電極と、前記ゲート電極と前記ソース/ドレイン電極とを絶縁させる層間絶縁膜とを含み、前記バッファ層、ゲート絶縁膜、及び層間絶縁膜は、非画素領域上の一部が除去された形態で位置し、前記除去された面積はパネル面積の8〜40%であることを特徴とする有機電界発光表示装置の製造方法に関する。

(もっと読む)

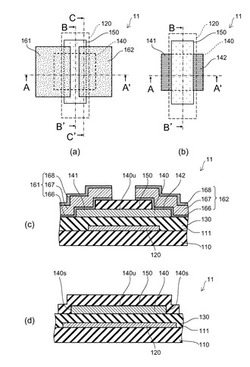

薄膜トランジスタ、その製造方法、表示装置及びその製造方法

【課題】熱処理による特性変動を抑制した酸化物半導体を用いた薄膜トランジスタ、その製造方法、表示装置及びその製造方法を提供する。

【解決手段】絶縁層と、前記絶縁層の上に設けられたゲート電極と、前記ゲート電極の上にゲート絶縁膜を介して設けられ、酸化物より形成された半導体層と、前記半導体層の上において、前記ゲート電極を挟むように離間して設けられたソース電極及びドレイン電極と、前記ソース電極及び前記ドレイン電極と、前記半導体層と、の間に設けられ、前記ゲート電極の上において、前記ソース電極及び前記ドレイン電極から露出した前記半導体層の側面の少なくとも一部を覆うチャネル保護層と、を備えたことを特徴とする薄膜トランジスタが提供される。

(もっと読む)

スプリットゲート・メモリセルの形成方法

方法は、半導体基板(12)上にゲート材料の第一層(18)を形成すること、第一層上にハードマスク層(20)を形成すること、開口(22)を形成すること、ハードマスク層上と開口内とに電荷蓄積層(24)を形成すること、電荷蓄積層上にゲート材料の第二層(26)を形成すること、ハードマスク層を被覆している、第二層の一部と電荷蓄積層の一部とを除去することであって、第二層の第二部分が開口内に残存している、除去すること、ハードマスク層上と第二部分上とに、第一ビットセル及び第二ビットセルの両方を画定するパターン化されたマスク層(28、30、32)を形成すること、パターン化されたマスク層を用いて第一ビットセル及び第二ビットセルを形成することを含み、第一ビットセル及び第二ビットセルはそれぞれ、第一層から形成された選択ゲート(38、40)と、第二層から形成された制御ゲート(34、36)とを含む。  (もっと読む)

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

1 - 20 / 34

[ Back to top ]