Fターム[5F110GG02]の内容

Fターム[5F110GG02]に分類される特許

7,141 - 7,158 / 7,158

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

D/A変換回路及び半導体装置

【課題】 高いビット数のデジタル信号に対応し、線形性が良く、占有面積の小さいD/A変換回路を提供する。

【解決手段】 複数の容量を有するD/A変換回路であって、複数の容量は、第1電極と、第1電極に接している第1誘電体と、第1誘電体に接している第2電極と、第2電極に接している第2誘電体と、第2誘電体に接している第3電極とをそれぞれ有しており、第2電極は、第1電極及び第3電極と重なっており、第2電極は、第1電極及び第3電極と重なっている部分において開口部を有しており、第2電極が有する開口部において、第1誘電体及び第2誘電体にコンタクトホールが形成されており、コンタクトホールを介して第1電極と第3電極が接続されていることを特徴とするD/A変換回路。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

電気光学装置及び電子機器

【課題】 液晶装置等の電気光学装置において、耐光性を高め、高品位の画像を表示する。

【解決手段】 電気光学装置は、TFTアレイ基板(10)上に、画素電極(9a)と、これに接続されたTFT(30)と、これに接続された配線(3a、6a)と、TFTの少なくともチャネル領域を上側から覆う上側遮光層(300、6a)と、このTFTの少なくともチャネル領域を下側から覆う下側遮光層(11a)とを備える。基板には、配線に対向する領域に格子状やストライプ状の溝(10cv)が掘られており、この溝内でチャネル領域に対向する領域に凹部(401)が更に掘られている。下側遮光膜は、該凹部内に形成されている。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 優れた特性を有する多結晶シリコン膜を備えた半導体装置を高い歩留まりで製造することが可能な半導体装置の製造方法を提供する。

【解決手段】 石英ガラスや無アルカリガラスなどの基板1上に、非晶質シリコン膜2aを形成する。その非晶質シリコン膜2a上にWシリサイド膜(導電膜)4bを形成する。そして、Wシリサイド膜(導電膜)4bに対し、高周波やYAGレーザービームなどの電磁波を照射することにより、Wシリサイド膜(導電膜)4bを発熱させ、この熱を利用して、非晶質シリコン膜2aを多結晶シリコン膜2に変える。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

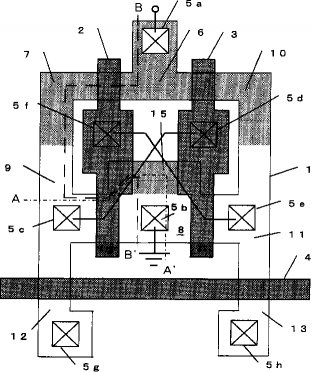

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】斜めからの入射光110、及び入射光110が乱反射を起こすことにより間接的に入射する光についても、遮光可能な薄膜トランジスタの構造及びその構造を工程数を増やすことなく簡易なプロセスで製造可能な製造方法を提供する。

【解決手段】 活性層となるpoly−Si膜104の両側のそれぞれにおいて、ゲート絶縁SiO2膜105及び下地SiO2膜103を遮光WSi2膜102が露出するまで選択的異方性エッチングし、コンタクト開口部106を形成する。その後、ゲートWSi2層107をスパッタ成膜し、さらに、フォトレジスト108をマスクとしてドライエッチングを実施し、ゲートWSi2電極111とWSi2からなるサイドウォール109を同時に形成する。これにより、サイドウォール109の下端を遮光WSi2膜102に接触させ上端をゲート絶縁SiO2膜105上面とほぼ同一高さに位置させる。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

多結晶シリコン薄膜の平坦化方法

【課題】 多結晶シリコン薄膜の表面に形成された突起を容易且つ確実に除去することができる多結晶シリコン薄膜の平坦化方法を提供することを目的とする。

【解決手段】 多結晶シリコン薄膜を炭素(C)とフッ素(F)と水素(H)とを少なくとも含有するガスのプラズマに曝すことにより突起を除去して多結晶シリコン薄膜の表面を容易且つ確実に平坦化することができる。

(もっと読む)

半導体装置、画像表示装置、半導体装置の製造方法、及び画像表示装置の製造方法

【課題】 CMOS−TFTを構成するp型及びn型TFTの各しきい値電圧を独立に効率良く(最小限のフォトリソグラフィーで)高精度に制御する。

【解決手段】 CMOS−TFTを製造するに際して、しきい値電圧(Vthp ,Vthn )制御として極低濃度にp型不純物(B:ボロン)の非選択的添加(p型及びn型TFTの双方に添加)及び選択的添加(n型TFTのみに添加)を連続的に行なう。具体的には、当初図4(a)のようにId −Vg 特性がp型及びn型TFT共に負シフトした状態から、非選択的添加により図4(b)のようにp型及びn型TFT共に正シフトさせてVthp を先ず仕様値とし、続いて選択的添加によりn型TFTのみ正シフトさせてVthn を仕様値に調整する。

(もっと読む)

積層金属配線及び薄膜トランジスタ基板、並びにそれらの製造方法

【課題】 IC等の半導体装置や、表示装置に用いられるTFT基板で使用される、Alを含む積層配線の信頼性を高める。

【解決手段】 上層の金属層22を下層のAl又はAlを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させる。この積層配線は、エッチングによりこれを作製する際に、上層の金属層22よりも下層のAl又はAlを含む合金の材料層21の方のエッチング速度を大きくして、Al又はAlを含む合金の材料層21のサイドエッチングを多くし、上層の金属層22を下層のアルミニウム又はアルミニウムを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させることで作製できる。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

7,141 - 7,158 / 7,158

[ Back to top ]