Fターム[5F110GG04]の内容

Fターム[5F110GG04]に分類される特許

81 - 100 / 1,414

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】ワイドギャップ半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

フォトセンサの駆動方法、半導体装置の駆動方法、半導体装置、及び電子機器

【課題】小型でコントラストの高い画像データを取得することができるフォトセンサを提供する。該フォトセンサを用いた半導体装置を提供する。

【解決手段】受光素子と、スイッチング素子であるトランジスタと、トランジスタを介して受光素子と電気的に接続する電荷保持ノードとを有するフォトセンサにおいて、導通状態から非導通状態とするためにトランジスタへ供給する駆動パルスの入力波形の立ち下がり時間を遅延させ、電荷保持ノードが保持する電荷の減少を抑制する。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】電気特性の低下や変動を生じにくい半導体装置とその製造方法を提供する。

【解決手段】ワイドバンドギャップ半導体層を半導体層に用いたトランジスタにおいて、水分・大気成分を透過しにくいパッシベーション性を有する絶縁層でワイドバンドギャップ半導体層を島状に分離する構造とする。該島状のワイドバンドギャップ半導体層の端部がその絶縁層と接する構成となるため、半導体層の端部からワイドバンドギャップ半導体層に水分・大気成分が侵入する現象を防止できる。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】非接触にて、被写体の位置情報の取得を容易に行うことができる固体撮像装置、または半導体表示装置の提供。

【解決手段】第1入射方向から第1入射角を有する光が入射する複数の第1フォトセンサと、第1入射方向とは異なる第2入射方向から第2入射角を有する光が入射する複数の第2フォトセンサとを有し、複数の第1フォトセンサのうち、第1入射方向の上流側の一つの第1フォトセンサの方が、第1入射方向の下流側の他の一つの第1フォトセンサよりも、第1入射角が大きく、複数の第2フォトセンサのうち、第2入射方向の上流側の一つの第2フォトセンサの方が、第2入射方向の下流側の他の一つの第2フォトセンサよりも、第2入射角が大きい。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

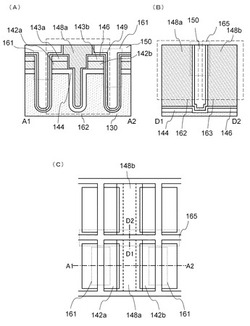

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体装置およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、下層側の第1導電体部および上層側の第2導電体部と、第1の導電体部と第2の導電体部との間に設けられた、厚膜状の絶縁体層と、この絶縁体層に対する貫通孔の内面形状に倣うように形成され、第1導電体部と第2導電体部とを電気的に接続するコンタクト部とを備え、貫通孔のテーパ角が鋭角となっている。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

81 - 100 / 1,414

[ Back to top ]