Fターム[5F110GG04]の内容

Fターム[5F110GG04]に分類される特許

21 - 40 / 1,414

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体の欠陥評価方法

【課題】ワイドギャップ半導体においても、CPM測定による欠陥密度の精度の高い評価を可能とする。

【解決手段】ワイドギャップ半導体のバンドギャップの波長(λEg)以下、所定の波長範囲以上におけるCPM測定で得られた照射光量から導出した吸収係数と、別途測定したワイドギャップ半導体のλEg以下の所定の波長範囲以上における吸収係数とのフィッティング値F(x)を0.0001以上1以下、好ましくは0.0001以上0.1以下とする。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】製造コストの低減、およびプロセス時間の短縮を可能とするfinFETの製造方法を提供する。

【解決手段】finFETは、ソース領域、ドレイン領域、およびソース領域とドレイン領域との間のチャネル領域を有するフィンを備えるように形成される。上記フィンは、半導体ウエハ上でエッチングされる。ゲートスタックは、上記チャネル領域に直接接触する絶縁層と、上記絶縁層に直接接触する導電性のゲート材料とを有するように形成される。上記ソース領域および上記ドレイン領域は、上記フィンの第一領域を露出するためにエッチングされる。次に、上記第一領域の一部が、ドーパントでドーピングされる。

(もっと読む)

電極被覆材料、電極構造体、及び、半導体装置

【課題】低いコンタクト抵抗、高い移動度を達成し得る半導体装置を提供する。

【解決手段】ゲート電極13、ゲート絶縁層14、有機半導体材料層から構成されたチャネル形成領域16、及び、金属から成るソース/ドレイン電極15を有する電界効果型トランジスタから成る半導体装置において、チャネル形成領域16を構成する有機半導体材料層と接するソース/ドレイン電極15の部分は、電極被覆材料21で被覆されており、電極被覆材料21は、金属イオンと結合し得る官能基、及び、金属から成るソース/ドレイン電極15と結合する官能基を有する有機分子から成る。

(もっと読む)

電子デバイスの製造方法

【課題】転写歩留まりを向上することが可能な電子デバイスの製造方法を提供することを目的とする。

【解決手段】薄膜トランジスタ(TFT)19の製造方法において、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aにガスバリア層7が形成されている。そのため、ガスバリア層7側からスタンプ5を空気で加圧する際に、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aから、半導体膜8および絶縁膜9が形成される面に、加圧した空気が抜けにくくなる。これにより、スタンプ5を基板1に押し付けることを持続することができるので、スタンプ5に形成された半導体膜8および絶縁膜9と基板1との密着性を増すことができる。したがって、基板1に転写されない半導体膜8および絶縁膜9が減少し、薄膜転写の歩留まりを向上させることができる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

化合物半導体の形成方法

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。

Si基板上のシリコン酸化膜の上に単結晶のSiC膜やGaN膜に形成したMOSFETなどの素子をアニールする手法を開示する。

【解決手段】光学ランプからの光をレンズで集光する手段、或いはレーザ光など高温度を発生させる手段によりSiCなど化合物半導体の表層部はSi基板の融点を越えるような高温度として、Si基板部はその融点よりも十分低い温度となるような冷却部を設けてSi基板を保持するステージを設けたことを特徴とするアニーリング装置。

(もっと読む)

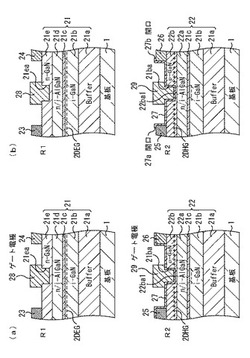

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

半導体装置

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1

の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するよ

うに、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるよう

に第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形

成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導

体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2

の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

21 - 40 / 1,414

[ Back to top ]