Fターム[5F110GG04]の内容

Fターム[5F110GG04]に分類される特許

121 - 140 / 1,414

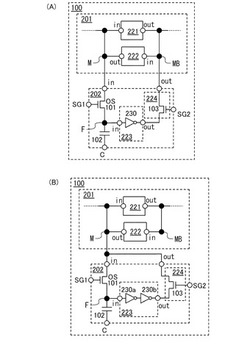

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、ゲート電極を形成後、インライン装置にて、酸化アルミニウム膜と酸化シリコン膜と酸化物半導体膜を大気暴露することなく連続的に形成し、さらに同インライン装置にて加熱および酸素添加処理を行い、他の酸化アルミニウム膜でトランジスタを覆った後、熱処理を行うことで、水素原子を含む不純物が除去され、且つ、化学量論比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】集積度が高く、データ保持時間の長い半導体記憶装置。

【解決手段】基板上の半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、第1のゲート電極および第1の導電膜の上面を露出し、第1のゲート電極および第1の導電膜の間に溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート電極、第1の導電膜および溝部と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

半導体装置の製造方法

【課題】高品質なIII族窒化物を結晶成長させ、高品質な半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】窒化サファイア基板をアルカリエッチングし、窒化サファイア基板を清浄化する。その後、III族窒化物を結晶成長させることにより、極めて高品質なN極性結晶を得ることができる。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

Ge・オン・III/V族・オン・インシュレータ構造を形成するための方法

【課題】半導体・オン・インシュレータ構造(10)を形成するための新規な方法を提供する。

【解決手段】本発明は、III/V族材料から作られる半導体層(3)を含む半導体・オン・インシュレータ構造(10)を形成するための方法に関し、(a)緩和ゲルマニウム層(2)をドナー基板(1)上に成長させるステップと、(b)III/V族材料から作られる少なくとも1つの層(3)をゲルマニウム層(2)上に成長させるステップと、(c)劈開面(6)を緩和ゲルマニウム層(2)内に形成するステップと、(d)ドナー基板(1)の劈開された部分を支持基板(4)に転写するステップであって、その劈開された部分が、劈開面(6)において劈開されたドナー基板(1)の一部分でありかつIII/V族材料から作られる少なくとも1つの層(3)を備える、ステップと、を備えることを特徴とする。

(もっと読む)

半導体装置及びその作製方法、ならびに電子機器

【課題】リーク電流が低減された半導体装置を提供すること。また、高い電界効果移動度と低いリーク電流が両立された半導体装置を提供すること。また、低消費電力化された電子機器を提供すること。また、マスク枚数を増やすことなくリーク電流を低減可能な、半導体装置の作製方法を提供すること。

【解決手段】高いキャリア移動度を有する半導体膜からなる半導体層の側面が、ソース電極及びドレイン電極と接しない構造とすればよい。また、フォトマスク数を増やすことなく、このような構成を有するトランジスタ構造を形成し、電子機器に適用すればよい。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したゲインセル方式の半導体メモリを提供する。

【解決手段】第1絶縁体101、読み出しビット線102b、第2絶縁体103、第3絶縁体103、第1半導体膜105、第1導電層107a乃至107d等を形成し、その上に凸状絶縁体112を形成する。そして、凸状絶縁体112を覆って、第2半導体膜114a、114bと第2ゲート絶縁膜115を形成する。その後、導電膜を形成し、これを異方性エッチングすることで、凸状絶縁体112の側面に書き込みワード線116a、116bを形成し、凸状絶縁体112の頂部に書き込みビット線125へ接続するための第3コンタクトプラグ124を形成する。このような構造でメモリセルの面積を最小で4F2とできる。

(もっと読む)

121 - 140 / 1,414

[ Back to top ]