Fターム[5F110GG19]の内容

Fターム[5F110GG19]の下位に属するFターム

超格子 (27)

Fターム[5F110GG19]に分類される特許

141 - 160 / 1,246

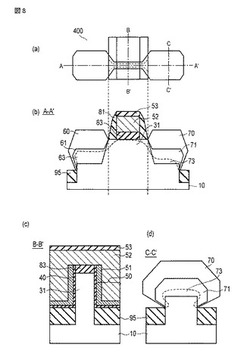

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

酸化物半導体膜、及び半導体装置

【課題】電気伝導度の安定した酸化物半導体膜を提供する。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む酸化物半導体膜において、酸化物半導体膜は、酸化物半導体膜の被形成面の法線ベクトルに平行な方向に揃うc軸配向した結晶領域を有し、c軸配向した結晶領域の組成が、In1+δGa1−δO3(ZnO)m(ただし、0<δ<1、m=1〜3)で表され、c軸配向した結晶領域を含む全体の酸化物半導体膜の組成が、InxGayO3(ZnO)m(ただし、0<x<2、0<y<2、m=1〜3)である。

(もっと読む)

配線構造およびスパッタリングターゲット

【課題】酸化物半導体層を備えた配線構造のスイッチング特性およびストレス耐性が良好であり、特にストレス印加前後のしきい値電圧変化量が小さく安定性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板上に少なくとも、ゲート絶縁膜、及び酸化物半導体層を有し、前記酸化物半導体層は、In、Ga、ZnおよびSnよりなる群から選択される少なくとも一種の元素(Z群元素)から構成される第1の酸化物半導体層、並びに、In、Ga、ZnおよびSnよりなる群から選択される少なくとも一種の元素(X群元素)と、Al、Si、Ti、Hf、Ta、Ge、WおよびNiよりなる群から選択される少なくとも一種の元素(Y群元素)を含む第2の酸化物半導体層を有する積層体であると共に、前記第2の酸化物半導体層は、前記第1の酸化物半導体層と前記ゲート絶縁膜との間に形成されている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

表示装置

【課題】簡便な構成及び動作によって表示装置の消費電力を低減すること。

【解決手段】表示装置が入力デバイスを備え、該入力デバイスから出力される画像操作信号に応じて、駆動回路に対する画像信号の入力を制御する。具体的には、入力デバイスが操作されない際の画像信号の入力頻度を、入力デバイスが操作される際の画像信号の入力頻度よりも低くする。これにより、当該表示装置が使用される際の表示の劣化(表示品質の低下)を抑制することが可能となり、且つ使用されない際の消費電力を低減することが可能になる。

(もっと読む)

光センシング装置及びその駆動方法

【課題】光センシング装置及びその駆動方法を提供する。

【解決手段】光センシング画素内の光センサートランジスタとスイッチトランジスタとが、それぞれ同じ構造の酸化物半導体トランジスタで形成される光センシング装置、及び前記光センシング装置の動作信頼性を向上させることができる駆動方法が提供される。光センシング装置によれば、光センシング画素内の光センサートランジスタとスイッチトランジスタとは、一つの基板上で同じ構造に隣接して形成され、スイッチトランジスタへの光の入射を防止するために、スイッチトランジスタの光入射面には光遮蔽膜がさらに配される。また、光センシング装置の駆動方法によれば、経時的なスイッチトランジスタのしきい電圧シフトを防止するために、光遮蔽膜には負(−)のバイアス電圧が印加される。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

フォトセンサ

【課題】低コスト化を図ることができるとともに、動作速度の向上を図ることができるフォトセンサを実現する。

【解決手段】複数の光電変換素子群201は行方向(X方向)に配置され、1つの光電変換素子群201は、行方向に対して略直交する列方向(Y方向)に並べられた3つのフォトダイオードPD1〜PD3を含む。さらに、各フォトダイオードから信号を読み出すための転送トランジスタ(Tr1〜Tr3)が設けられる。同一行に属する転送トランジスタのゲート電極(2241,2242,2243)は一体的に形成される。さらに、ソース電極223とゲート電極との重なり部分の面積は、ドレイン電極222とゲート電極との重なり部分の面積よりも小さい。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】有機半導体層の移動度を低下させることなく、容易に有機半導体層をパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供する。

【解決手段】液晶性有機半導体材料を配向させる配向層1上にソース電極2およびドレイン電極3を形成するソース電極およびドレイン電極形成工程と、上記ソース電極および上記ドレイン電極を覆うように上記配向層上に、液晶性有機半導体材料を有する有機半導体層4を形成する有機半導体層形成工程と、上記有機半導体層上の少なくとも上記ソース電極および上記ドレイン電極間のチャネル領域C上に、誘電体層5を形成する誘電体層形成工程と、上記誘電体層が形成された上記有機半導体層を上記液晶性有機半導体材料の液晶相温度でアニール処理するアニール処理工程と、を有することを特徴とする有機半導体素子の製造方法。

(もっと読む)

グラフェン電子素子及び製造方法

【課題】グラフェン電子素子及び製造方法を提供する。

【解決手段】ゲート電極として作用する導電性基板と、基板上に配置されたゲートオキサイドと、ゲートオキサイド上で互いに離隔された一対の第1金属と、第1金属上で、第1金属の間に延びたグラフェンチャネル層と、グラフェンチャネル層の両端にそれぞれ配置されたソース電極及びドレイン電極と、を備えるグラフェン電子素子である。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と接して形成される絶縁膜へのインジウムの拡散を抑え、また、酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜と接する絶縁膜との界面特性を良好にし、安定した電気的特性を有し、信頼性の高い半導体装置を提供する。

【解決手段】インジウムを含む酸化物半導体膜において、表面のインジウム濃度を低減させることによって、酸化物半導体膜の上に接して形成される絶縁膜へのインジウムの拡散を防ぐ。また、さらに酸化物半導体膜表面のインジウム濃度を低減させることによって、表面にインジウムを実質的に含まない層を形成することができ、この層を絶縁膜の一部とすることにより、酸化物半導体膜と、該酸化物半導体膜と接する絶縁膜との界面特性を良好にする。

(もっと読む)

電子デバイス及びその製造方法

【課題】転写プロセスを用いずに、所期のグラフェンを制御性良く容易且つ確実に安定形成し、信頼性の高い高性能の微細な電子デバイスを実現する。

【解決手段】基板1上に絶縁層2を形成し、絶縁層2に空隙2Aを形成し、空隙2Aに触媒材料4を充填し、絶縁層2における触媒材料4の露出面4aにグラフェン5を形成し、絶縁層2上でグラフェン5の両端部に接続するように一対の電極5,6を形成し、グラフェン5を一部除去してグラフェンリボン8を形成し、グラフェンリボン8の除去された部位である間隙2A1,2A2を通じて触媒材料4を除去する。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を介して対向する一対の第2の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられるゲート絶縁膜と、ゲート絶縁膜上に設けられて、かつ第1の領域に重畳する第1の電極と、を有し、第1の領域は、c軸配向した結晶部を有する非単結晶の酸化物半導体領域であり、一対の第2の領域は、ドーパントを含んで、かつ複数の結晶部を有する酸化物半導体領域であることを特徴とする半導体装置である。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

141 - 160 / 1,246

[ Back to top ]