Fターム[5F110GG19]の内容

Fターム[5F110GG19]の下位に属するFターム

超格子 (27)

Fターム[5F110GG19]に分類される特許

161 - 180 / 1,246

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を介して対向する一対の第2の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられるゲート絶縁膜と、ゲート絶縁膜上に設けられて、かつ第1の領域に重畳する第1の電極と、を有し、第1の領域は、c軸配向した結晶部を有する非単結晶の酸化物半導体領域であり、一対の第2の領域は、ドーパントを含んで、かつ複数の結晶部を有する酸化物半導体領域であることを特徴とする半導体装置である。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

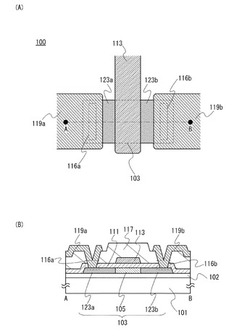

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

化合物及び該化合物を用いてなる薄膜

【課題】溶媒に対する溶解性が高い化合物を提供する。

【解決手段】第1の2価の構造単位と第2の2価の構造単位とを有し、該第1の2価の構造単位がベンゼン環、シクロヘキサン環及びヘテロ原子を有する5員環あるいはベンゼン環と縮合し、シクロヘキサン環が橋架けされている特定の縮合環構造を有し、ヘテロ原子を有する5員環あるいはベンゼン環で連結する構造単位であり、該第2の2価の構造単位が、上記の構造単位とは異なる構造単位である化合物。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

Ge・オン・III/V族・オン・インシュレータ構造を形成するための方法

【課題】半導体・オン・インシュレータ構造(10)を形成するための新規な方法を提供する。

【解決手段】本発明は、III/V族材料から作られる半導体層(3)を含む半導体・オン・インシュレータ構造(10)を形成するための方法に関し、(a)緩和ゲルマニウム層(2)をドナー基板(1)上に成長させるステップと、(b)III/V族材料から作られる少なくとも1つの層(3)をゲルマニウム層(2)上に成長させるステップと、(c)劈開面(6)を緩和ゲルマニウム層(2)内に形成するステップと、(d)ドナー基板(1)の劈開された部分を支持基板(4)に転写するステップであって、その劈開された部分が、劈開面(6)において劈開されたドナー基板(1)の一部分でありかつIII/V族材料から作られる少なくとも1つの層(3)を備える、ステップと、を備えることを特徴とする。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

半導体装置及びその作製方法、ならびに電子機器

【課題】リーク電流が低減された半導体装置を提供すること。また、高い電界効果移動度と低いリーク電流が両立された半導体装置を提供すること。また、低消費電力化された電子機器を提供すること。また、マスク枚数を増やすことなくリーク電流を低減可能な、半導体装置の作製方法を提供すること。

【解決手段】高いキャリア移動度を有する半導体膜からなる半導体層の側面が、ソース電極及びドレイン電極と接しない構造とすればよい。また、フォトマスク数を増やすことなく、このような構成を有するトランジスタ構造を形成し、電子機器に適用すればよい。

(もっと読む)

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

含ピロールヘテロアセン化合物、該化合物の製造方法、該化合物を含む薄膜及び該薄膜を含む有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

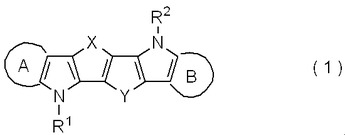

【解決手段】式(1)

(式中、X及びYは、硫黄原子、酸素原子、セレン原子、テルル原子又はSO2を表す。環構造A及び環構造Bは、芳香族炭化水素環又は芳香族複素環を表す。該芳香族複素環は単一の環構造である。

R1およびR2は、水素原子、炭素数1〜30のアルキル基、炭素数1〜30のアルコキシ基、炭素数2〜30のアルケニル基、炭素数2〜30のアルキニル基、炭素数1〜30のアルキルチオ基、炭素数6〜20のアリール基、炭素数4〜20のヘテロアリール基を表す。)

で表される含ピロールヘテロアセン化合物。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オフ電流を抑えるための側壁酸化膜を有する表示装置と、その製造方法を提供することを目的とする。

【解決手段】

ゲート電極GTと、ゲート電極GTの上側に島状に形成される半導体層Sと、半導体層Sの側面に形成される側壁酸化膜OWと、半導体層Sの側方から延伸して半導体層Sの上側に形成されるドレイン電極DTおよびソース電極STと、を有する表示装置であって、側壁酸化膜OWは、2.1nm以上の厚みを有する、ことを特徴とする表示装置。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

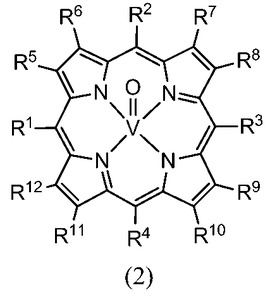

テトラビシクロポルフィリンバナジル錯体の製造方法、半導体層形成用組成物、電子デバイスの製造方法、太陽電池及び太陽電池モジュール

【課題】電子デバイスで好適に用いられるテトラベンゾポルフィリンバナジル錯体の高純度製造法の提供。

【解決手段】テトラビシクロポルフィリン化合物とバナジル化合物の反応を65℃以上95℃以下の温度で行う。式(2)の錯体の製造方法。 (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート部におけるリーク電流が低減できる反面、プロセス上の制約があるため製造が困難で、ゲートリーク電流を安定して低減させることが困難だった。

【解決手段】基板と、前記基板上に形成され且つ二次元キャリアガスを有する半導体機能層と、前記半導体機能層上において互いに離間して形成される第1及び第2の主電極と、前記半導体機能層上における前記第1及び第2の主電極間に形成される制御電極と、前記半導体機能層と前記制御電極との間に形成される金属酸化膜と、を備え、

前記金属酸化膜と前記半導体機能層との接合界面における結晶格子は不連続であることを特徴とする半導体装置。

(もっと読む)

161 - 180 / 1,246

[ Back to top ]