Fターム[5F110HJ30]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | その他 (157)

Fターム[5F110HJ30]に分類される特許

61 - 80 / 157

半導体装置及びその作製方法

【課題】微小なコンタクトホールを形成し、集積回路を微細化することを目的とする。

【解決手段】スイッチング素子および各配線を覆う層間絶縁膜111として有機材料を用い、且つ、金属膜112のマスクを用い、ドライエッチング法によってコンタクトホールを形成し、配線114を形成する。

(もっと読む)

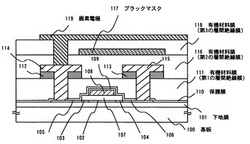

発光装置

【課題】鮮明な多階調カラー表示の可能な発光装置及びそれを具備する電気器具を提供する。

【解決手段】画素104に設けられたEL素子109の発光、非発光を時間で制御する時分割駆動方式により階調表示を行い、電流制御用TFT108の特性バラツキによる影響を防ぐ。また、基板上に形成されるTFT自体も各回路又は素子が必要とする性能に併せて最適な構造のTFTを配置することで、信頼性の高いアクティブマトリクス型発光装置を実現することができる。このようなアクティブマトリクス型発光装置を表示ディスプレイとして具備することで、画像品質が良く、信頼性の高い高性能な電気器具を生産することが可能となる。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体装置及び電子機器

【課題】逆スタガ型TFTにおいて、薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、前記第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、前記活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】セルフアライン構造の薄膜トランジスタの特性を安定させることが可能な薄膜トランジスタおよびその製造方法、並びに表示装置を提供する。

【解決手段】酸化物半導体膜20のチャネル領域20A上にゲート絶縁膜30およびゲート電極40をこの順に同一形状で形成する。酸化物半導体膜20,ゲート絶縁膜30およびゲート電極40の上に金属膜を形成し、この金属膜に対して熱処理を行うことにより、金属膜を酸化させて高抵抗膜50を形成すると共に、ソース領域20Sおよびドレイン領域20Dの上面から深さ方向における少なくとも一部に低抵抗領域21を形成する。低抵抗領域21は、アルミニウム(Al)等をドーパントとして含むか、またはチャネル領域20Aよりも酸素濃度が低いことにより低抵抗化されている。変動要素の多いプラズマ処理を用いずに高抵抗領域21を形成可能となり、安定した特性が得られる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】容易に製造することができ、かつ信頼性の高い薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極、ゲート絶縁膜および活性層し、活性層上に第1の保護層となるGa酸化物膜を形成する。Ga酸化物膜上に第2の保護層となる感光性有機系絶縁膜を形成し、感光性有機系絶縁膜においてチャネル領域に整合する部分をパターン部とし、それ以外の部分を非パターン部とする。この非パターン部を除去し、この非パターン部の除去とともにパターン部をマスクとして非パターン部下のGa酸化物膜を除去して、第1の保護層および第2の保護層を形成しチャネル保護膜を得る。チャネル保護膜を覆うようにソース電極およびドレイン電極となる膜を形成し、この膜上にレジストパターンを形成し、チャネル保護膜をエッチングストッパとして膜をエッチングし、ソース電極およびドレイン電極を形成する。

(もっと読む)

半導体膜の作製方法

【課題】量産性に優れた薄膜トランジスタを提供する。また半導体装置の作製において有

用な半導体薄膜を提供する。

【解決手段】プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を形成し、前記半導体膜の一部を除去して、活性層を

形成し、トップゲート型薄膜トランジスタまたはボトムゲート型薄膜トランジスタを作製

する。また、プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を剥離層として用いた半導体装置を作製する。また、

プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1×1021/

cm3で含む半導体膜をゲッタリングサイトとして用いた半導体装置を作製する。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造方法によって製造された良好なTFT特性を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、絶縁基板11と、絶縁基板11に支持されたチャネル領域33A、ソース領域34Aおよびドレイン領域35Aを含む半導体層30Aと、チャネル領域33Aの導電性を制御するゲート電極51とを有する。半導体層30Aは、チャネル領域33Aとソース領域34Aとの間に形成された第1低濃度領域31A、および、チャネル領域33Aとドレイン領域35Aとの間に形成された第2低濃度領域32Aとを有する。チャネル領域33A、第1および第2低濃度領域31Aおよび32Aは、ソースおよびドレイン領域34Aおよび35Aの不純物濃度より低い第1不純物濃度を有する。ゲート電極51は、第1および第2低濃度領域31Aおよび32Aの全部を覆うように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】フィン型半導体領域を有する半導体装置において所望の特性が得られるようにする。

【解決手段】支持基板11上に、上面及び側面を有する第1の半導体領域13a〜13dを形成する。第1の半導体領域13a〜13dに第1導電型の不純物をプラズマドーピング法によって注入し、それにより、第1の半導体領域13a〜13dの上部に第1の不純物領域17aを形成すると共に、第1の半導体領域13a〜13dの側部に第2の不純物領域17bを形成する。このとき、注入ドーズ量が第1のドーズ量となる第1の条件でプラズマドーピング法を実施した後、注入ドーズ量が第1のドーズ量よりも小さい第2のドーズ量となる第2の条件でプラズマドーピング法を実施する。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

電圧調整回路

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ゲートがソース又はドレインに電気的に接続され、ソース及びドレインの一方に第1の信号が入力され、チャネル形成層としてキャリア濃度が5×1014/cm3以下である酸化物半導体層を有するトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極にクロック信号である第2の信号が入力される容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性が得られるフィン型半導体領域を有する半導体装置を実現する。

【解決手段】上面及び側面を有する第1の半導体領域61の上部に第1導電型の第1の不純物領域61aが形成されていると共に、第1の半導体領域61の側部に第1導電型の第2の不純物領域61bが形成されている。第1の半導体領域61の所定の部分における少なくとも側面及び上部コーナーを覆うようにゲート絶縁膜62が形成されている。ゲート絶縁膜62の外側に位置する部分の第1の半導体領域61における上部コーナーの曲率半径r’は、ゲート絶縁膜62の下側に位置する部分の第1の半導体領域61における上部コーナーの曲率半径rよりも大きく且つ2r以下である。

(もっと読む)

薄膜トランジスタおよび電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】ソース電極4およびドレイン電極5は、互いに離間されていると共にそれぞれ有機半導体層3の上に重なっている。有機半導体層3における有機半導体分子の配向状態は、ソース電極4およびドレイン電極5に重なっている部分P1,P2と重なっていない部分P3との間において異なっている。有機半導体層3の厚さ方向における部分P1,P2の電気抵抗R1Y,R2Yは、同方向における部分P3の電気抵抗R3Yよりも小さくなっている。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

表示装置及び電子機器

【課題】表示装置に置いて、多階調表示を実現することを目的とする。

【解決手段】トランジスタ及び表示素子を有する画素がマトリクス状に配置された画素部と、前記トランジスタのゲートに電気的に接続されたゲートドライバと、前記トランジスタのソース又はドレインに電気的に接続されたソースドライバと、前記ソースドライバに信号を出力するデータ処理回路とを有し、前記トランジスタは、酸化物半導体を用いており、前記データ処理回路は、入力されるmビットのデジタルデータのうち、nビットのデジタルデータ(m、nは共に正の整数、かつm>n)を電圧階調に用い、(m−n)ビットのデジタルデータを時間階調に用いる表示装置である。

(もっと読む)

61 - 80 / 157

[ Back to top ]