Fターム[5F110HL07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | 透明導電膜(例;ITO) (1,570)

Fターム[5F110HL07]に分類される特許

41 - 60 / 1,570

液晶表示装置及びその不良画素修復方法

【課題】本発明は、液晶表示装置及びその不良画素の修復方法を提供する。

【解決手段】第1の絶縁基板と、第1の絶縁基板上に実質的に第1の方向に互いに平行するように配値されたゲート配線およびストレージ配線と、ゲートおよびストレージ配線と絶縁されて交差し、実質的に第2の方向に配値されたデータ配線と、データ配線上に形成された保護膜と、保護膜上に形成された第1の画素電極と第2の画素電極と、第1の画素電極に隣接する第2の画素電極を含み、ストレージ配線は、実質的に第1の方向に配値された水平部および水平部から実質的に第2の方向に分枝し、データ配線とオーバーラップする垂直部を含み、垂直部は、第1の画素電極および第2の画素電極とオーバーラップし、第1の画素電極と垂直部がオーバーラップする幅は第2の画素電極および垂直部の間のオーバーラップする幅と実質的に同一であることを特徴とする液晶表示装置。

(もっと読む)

表示装置

【課題】高開口率を有し、容量の大きな保持容量を有する表示装置を提供する。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

(もっと読む)

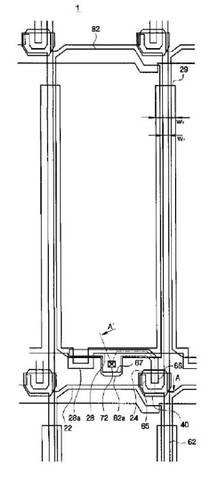

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

薄膜トランジスタの製造方法

【課題】印刷法を用いて薄膜トランジスタを製造する場合において、前処理などを必要とせずに微細パターンを形成可能であり、トランジスタ特性の面内均一性に優れるとともに、インキの利用効率に優れた薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性の基板上に形成されたゲート電極41、ゲート絶縁膜、ソース電極43、ドレイン電極44、半導体層45及び封止層46を有する薄膜トランジスタ1を製造する薄膜トランジスタの製造方法であって、インキ供給手段を用いて凹凸パターンが形成された印刷用版にインキを供給するインキ供給工程と、インキの予備乾燥を経た後に凸版を用いて非画線部のインキ液膜を除去するインキ液膜除去工程と、印刷用版上に残った画線部のインキ液膜を基板40に転写して、半導体層45及び封止層46のうち少なくとも一方を形成するインキ液膜転写工程を有する。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置、発光装置、及び電子機器

【課題】動作不良を抑制する。

【解決手段】電界効果トランジスタと、スイッチと、容量素子と、を設ける。電界効果トランジスタは、チャネル形成領域を介して互いに重畳する第1のゲート及び第2のゲートを有し、第2のゲートの電位に応じて閾値電圧の値が変化する。スイッチは、電界効果トランジスタのソース及びドレインの一方と、電界効果トランジスタにおける第2のゲートと、を導通状態にするか否かを制御する機能を有する。容量素子は、電界効果トランジスタにおける第2のゲートと電界効果トランジスタにおけるソース及びドレインの他方との間の電圧を保持する機能を有する。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

薄膜トランジスタアレイ、薄膜トランジスタアレイの製造方法、画像表示装置

【課題】高開口率を得るために形成する層間絶縁膜のパターニング性、歩留まりを向上させ、生産性に優れた薄膜トランジスタアレイを提供する。

【解決手段】ゲート絶縁膜2上には、ゲート電極11に重なる位置に、ドレイン電極16と、ソース電極17と、を隔てて設けてあり、ドレイン電極16には、画素電極15を接続し、ソース電極17には、ソース配線18を接続してある。また、ゲート絶縁膜2上には、ドレイン電極16及びソース電極17の双方に重なるように、半導体層3を設けてある。ゲート絶縁膜2上には、画素電極15の一部を露出させた状態で、ソース電極17、ソース配線18、ドレイン電極16、画素電極15、半導体層3を封止する一層目封止層4を設け、一層目封止層4上には、ソース電極17及びソース配線18に重なる位置に、二層目封止層5を設けてある。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板

【課題】理論的根拠に基づいて酸化物半導体の母材料に添加される物質を使用することによって、優れた特性を有する酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板を提供する。

【解決手段】 本発明の一実施形態に係る酸化物半導体は、亜鉛(Zn)及び錫(Sn)のうちの少なくとも一つの元素を含む第1物質、及び前記第1物質に添加される第2物質を含み、前記第1物質と酸素(O)との電気陰性度差値から前記第2物質と酸素(O)との電気陰性度差値を引いた値が1.3以下であることを特徴とする。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】高い移動度を実現でき、且つ、ストレス耐性(ストレス印加前後のしきい値電圧シフト量が少ないこと)にも優れた薄膜トランジスタ用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、Zn、Sn、およびInと;Si、Hf、Ga、Al、Ni、Ge、Ta、W、およびNbよりなるX群から選択される少なくとも一種の元素(X群元素)と、を含むものである。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

トランジスタ

【課題】新たな半導体材料を用いたトランジスタを提供する。

【解決手段】水素濃度が1×1016cm−3以下の領域を有する酸化物半導体層又はキャリア密度が1×1014cm−3未満の領域を有する酸化物半導体層を有し、酸化物半導体層の膜厚は、酸化物半導体層のドナー密度に基づく空乏層の広がり得る最大幅よりも薄いトランジスタである。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、現在実用化されている量産技術からの膜構成、プロセス条件、または生産装置等の変更が少なく、半導体装置に安定した電気特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、を有し、ゲート絶縁膜は、窒化酸化シリコン膜と、窒化酸化シリコン膜上に形成された酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された金属酸化膜と、を含み、金属酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

41 - 60 / 1,570

[ Back to top ]