Fターム[5F110HL07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | 透明導電膜(例;ITO) (1,570)

Fターム[5F110HL07]に分類される特許

21 - 40 / 1,570

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置、及びその作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置を提供する。また、微細化された半導体装置を歩留まりよく提供する。

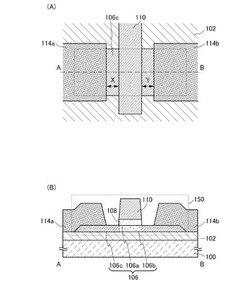

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体膜と、酸化物半導体膜の側面に接して設けられ、かつ酸化物半導体膜よりも膜厚が大きいソース電極層及びドレイン電極層と、酸化物半導体膜、ソース電極層、及びドレイン電極層上に設けられたゲート絶縁膜と、酸化物半導体膜の上面と、ソース電極層及びドレイン電極層の上面との間に生じた段差により生じた凹部に設けられたゲート電極層と、を有する構造である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

液晶表示装置

【課題】画質の低下を防ぎつつ、消費電力の低減を実現することができる、液晶表示装置

の駆動方法を提案する。

【解決手段】液晶素子と、当該液晶素子への画像信号の供給を制御するトランジスタとを

画素に有する。上記トランジスタは、チャネル形成領域に、シリコン半導体よりもバンド

ギャップが広く、真性キャリア密度がシリコンよりも低い半導体を含み、オフ電流の極め

て小さい。そして、画素を反転駆動させる際に、画素電極を間に挟んで配置されている一

対の信号線に、互いに逆の極性を有する画像信号を入力する。上記構成により、液晶素子

に容量素子を接続しなくても、表示される画質が低下するのを防ぐ。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】チャネル長方向の一方の側面においてソース電極層と接し、チャネル長方向の他方の側面においてドレイン電極層と接する酸化物半導体層を含むトランジスタとすることでソース電極層とドレイン電極層の間の電界を緩和して、短チャネル効果を抑制する。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

保護膜溶液組成物、薄膜トランジスター表示板及び薄膜トランジスター表示板の製造方法

【課題】保護膜溶液組成物を提供すること。

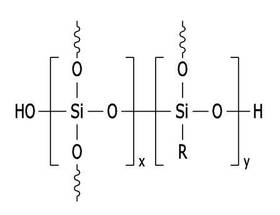

【解決手段】下記の化学式1で表わされる有機シロキサン樹脂を含む保護膜溶液組成物:

・・・化学式1

(式中、Rは1乃至25個の炭素を有する飽和炭化水素または不飽和炭化水素から選ばれた少なくとも一つの置換基であり、x、yはそれぞれ1乃至200であり、各波線は水素原子、xシロキサン単位またはyシロキサン単位との結合を示すか、あるいは、xシロキサン単位、yシロキサン単位またはこれらの組み合わせを含む他の有機シロキサン鎖のxシロキサン単位またはyシロキサン単位との結合を示す)。

(もっと読む)

駆動用回路基板およびその製造方法並びに表示装置および電子機器

【課題】工程数が少なく、且つ、材料の利用効率が向上した駆動用回路基板およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本開示の表示装置は、一対のソース・ドレイン電極と、チャネル領域を形成すると共に、ソース・ドレイン電極に接して設けられた有機半導体層と、ソース・ドレイン電極まで貫通する貫通孔を有すると共に、有機半導体層およびソース・ドレイン電極上に設けられた少なくとも1層からなる絶縁層と、チャネル領域に対応する位置に設けられたゲート電極と、貫通孔を介して前記ソース・ドレイン電極に電気的に接続されると共に、ゲート電極と同一材料、且つ、同一膜厚で絶縁層上に設けられた画素用電極とを備える。

(もっと読む)

薄膜トランジスタアレイ基板の製造方法

【課題】 有機樹脂膜を有するTFTアレイ基板の製造工程において、ブラシ洗浄の際に異物が有機平坦化膜表面にキズを生じさせることがある。このようにキズが生じた有機平坦化膜上に、画素電極となる透明電極膜を成膜した場合、キズ上の透明電極膜も断線してしまい、画素電極に信号が伝わらず表示不良を引き起こすことがある。

【解決手段】 有機平坦化膜を塗布する工程と、中間調露光を用いて有機平坦化膜に凹凸を形成する工程と、凹凸が形成された有機平坦化膜表面をロールブラシを用いて洗浄する工程と、洗浄工程後に、有機平坦化膜上に画素電極を構成する透明導電膜を成膜する工程とを備えた薄膜トランジスタアレイ基板の製造方法を提供する。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

21 - 40 / 1,570

[ Back to top ]