Fターム[5F110HL24]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 電極、配線の製法 (3,290) | 堆積 (3,000) | CVD (584)

Fターム[5F110HL24]に分類される特許

141 - 160 / 584

表示装置

【課題】本発明では、高画質で信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】本発明は、画素領域における画素電極層上、及び画素電極層周辺を覆う隔壁として機能する絶縁層上に、スペーサを有する。このスペーサによって、発光材料を画素電極層上に形成する際、選択的に形成するためのマスクは支持され、マスクのよじれやたわみなどによって画素電極層に接することを防止する。よって、画素電極層にはマスクによる傷などの損傷が生じず、画素電極層は形状不良とならないので、高繊細な表示を行う、高信頼性な表示装置を作製することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留まりの低下を抑制する半導体装置及びその製造方法を提供する。

【解決手段】実施の形態の半導体装置1は、配線20を有する配線層11bと、配線層11b上に形成された層間絶縁膜26と、層間絶縁膜26上に形成され、上部がシリサイド化されたアモルファスシリコン層27を有するTFT14と、TFT14上に、層間絶縁膜47を介して形成された配線50を有する配線層12aと、層間絶縁膜47、アモルファスシリコン層27及び層間絶縁膜26を貫通し、第1及び第2の配線を電気的に接続するコンタクトプラグ32と、を備える。

(もっと読む)

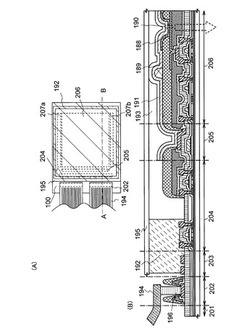

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】互いに異なる形態の薄膜トランジスタを効率よく作り分けること。

【解決手段】厚さ方向にシリコンの結晶化度が異なる第1領域と第2領域とを有する半導体層を有し、ボトムゲート構造の駆動トランジスタ6と、トップゲート構造のスイッチトランジスタ5とを形成する際、基板10と第1絶縁膜11の間に駆動トランジスタ6の第1ゲート電極6aを形成する工程と、第2保護絶縁膜5d上にスイッチトランジスタ5の第2ゲート電極5aを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、駆動トランジスタ6の第1ゲート電極6aと、スイッチトランジスタ5の第2ゲート電極5aを形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分ける。

(もっと読む)

半導体基板の作製方法、及び半導体装置の作製方法

【課題】絶縁表面に欠陥の少ない単結晶半導体膜を有する半導体基板の、簡便な作製方法を提供することを課題の一つとする。また、歩留まりの良い半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】単結晶半導体基板の表面に絶縁層を形成し、絶縁層をエッチングしながら、絶縁層を介して単結晶半導体基板にイオン照射を行うことで、脆化領域を形成し、単結晶半導体基板の表面に接合層を形成し、単結晶半導体基板と、支持基板とを、接合層を介して貼り合わせ、熱処理を行うことにより、脆化領域内に劈開面を形成して、単結晶半導体基板の一部を分離する、半導体基板の作製方法を提供する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース領域またはドレイン領域と、が、導電層および第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、をそれぞれ異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体装置

【課題】生産性の高い半導体材料を用い、且つ耐圧性を向上させたトランジスタを提供することを課題の一とする。または、高耐圧のトランジスタを用いた大電力向けの半導体装置を提供することを課題の一とする。

【解決手段】トランジスタにおいて、高電界の印加されるドレイン電極を平坦な面上に形成し、且つ、ゲート電極の、チャネル幅方向のドレイン電極側の端部、およびチャネル長方向の端部を、ゲート絶縁層を介して酸化物半導体層で覆うことによって、トランジスタの耐圧を向上させる。また、該トランジスタを用いた大電力向けの半導体装置を提供することができる。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

垂直型ナノチューブ半導体デバイス構造体の形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブ14を組み組む垂直型デバイス構造体42を製造する方法である。各々のナノチューブ14は、触媒パッド10によって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料22のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極30の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタ構造50を作ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

半導体基板、半導体装置、および半導体装置の製造方法

【課題】半導体装置の製造工程において、十分にゲッタリング効果を得ることができる半導体基板を提供する。

【解決手段】半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7と、を備えることを特徴とする半導体基板3を提供する。また、半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7を備える半導体基板3と、前記半導体層7上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記半導体層7内であって、前記ゲート電極に対して自己整合となる位置に設けられた不純物拡散領域と、を有することを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

半導体基板の保持用トレイ、並びに半導体基板および半導体装置の作製方法

【課題】複数枚の絶縁層被覆単結晶半導体基板に対して効率よくイオン注入を行い、大面積の単結晶半導体層を備えた半導体基板の作製方法を提供することを課題の一とする。

【解決手段】半導体基板の作製工程において、表面のファンデルワールス力を調整した保持用トレイに表面に絶縁層が形成された複数枚の単結晶半導体基板を貼り合わせ、複数枚の単結晶半導体基板にイオン照射工程を行うことで複数枚の単結晶半導体基板の所定の深さに脆化層を形成し、複数枚の単結晶半導体基板にファンデルワールス力を調整したベース基板を貼り合わせることでファンデルワールス力の差を利用して保持用トレイを選択的に分離し、剥離加熱処理を行い劈開面を形成して単結晶半導体基板をベース基板から分離することにより、絶縁層を介して単結晶半導体基板をベース基板に転載する。

(もっと読む)

141 - 160 / 584

[ Back to top ]