Fターム[5F110HM07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | チャネル領域と結晶構造が異なるもの (172)

Fターム[5F110HM07]に分類される特許

21 - 40 / 172

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】バックチャネル部の表面のアルミニウム汚染に起因する漏れ電流を抑制を防止でき、高い信頼性と、高い歩留を実現できる構造の薄膜トランジスタを提供することを目的とする。

【解決手段】この発明に係る薄膜トランジスタは、シリコンを半導体層とするバックチャネル部を有するボトムゲート構造の薄膜トランジスタであって、アルミニウムを含むソース電極またはドレイン電極と、バックチャネル部の一部であって半導体層の表層を覆うサイアロン化合物の層とを有するものである。

(もっと読む)

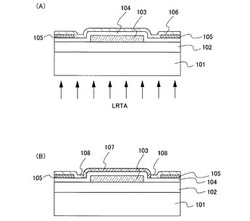

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

発光装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にp型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する第1の微結晶半導体膜を酸化絶縁膜上に形成した後、第2の条件により混相粒を結晶成長させて混相粒の隙間を埋めるように、第1の微結晶半導体膜上に第2の微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を50倍以上1000倍以下にして堆積性気体を希釈し、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を100倍以上2000倍以下にして堆積性気体を希釈し、処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

電界効果トランジスタ(FET)およびそれを形成する方法

薄膜トランジスタとその製造方法と電気光学装置と電子機器

【課題】 非晶質シリコンTFTの特性を大幅に向上させつつ、その製造プロセスにおける膜飛びを抑制する。

【解決手段】まず、基板10上にゲート電極11を形成する。次に、基板10上に、ゲート電極11を平面視で覆うゲート絶縁膜12を形成し、その上に、チャネル領域13cとソース領域13sとドレイン領域13dとを有する非晶質の半導体膜13を形成し、その上に、チャネル領域13cを平面視で覆うチャネル保護層14を形成する。次に、半導体膜13とチャネル保護層14とにレーザーを照射することにより、チャネル領域13cを微結晶化する。次に、半導体膜13上に、チャネル保護層14を平面視で覆い、ソース領域13sとドレイン領域13dとに平面視で重なる導電膜を形成する。次に、導電膜をエッチングしてソース電極16sとドレイン電極16dとを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

薄膜トランジスタおよび電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】ソース電極4およびドレイン電極5は、互いに離間されていると共にそれぞれ有機半導体層3の上に重なっている。有機半導体層3における有機半導体分子の配向状態は、ソース電極4およびドレイン電極5に重なっている部分P1,P2と重なっていない部分P3との間において異なっている。有機半導体層3の厚さ方向における部分P1,P2の電気抵抗R1Y,R2Yは、同方向における部分P3の電気抵抗R3Yよりも小さくなっている。

(もっと読む)

非晶質半導体膜の結晶化方法、薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法

【課題】特性の優れた半導体膜を簡便に得ることができる微結晶半導体膜の結晶化方法と、これを応用した薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、基板1上に形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3を介してゲート電極2の対面に形成され、ソース領域となる第1非晶質領域41、ドレイン領域となる第2非晶質領域42、及び第1非晶質領域41と第2非晶質領域42との間に配置されたチャネル領域となる結晶性領域43を有する半導体膜4と、半導体膜4上に結晶性領域43と直接接触することなく形成され、ソース領域及びドレイン領域とそれぞれ電気的に接続されたソース電極81及びドレイン電極82と、を備えるものである。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに半導体装置

【課題】薄膜トランジスタのリーク特性を維持しつつ、オン電流を大幅に改善することができる薄膜トランジスタ及びその製造方法並びに半導体装置の製造方法を提供すること。

【解決手段】半導体薄膜を形成する工程と、前記半導体薄膜にシリコンを注入する工程と、チャネル形成領域とソース形成領域及びドレイン形成領域との間にそれぞれ位置するLDD形成領域上にマスクを形成する工程と、前記LDD形成領域上にマスクを形成した半導体薄膜上にシリコンを注入する工程と、前記半導体薄膜を熱処理により結晶化する工程と、を有する薄膜トランジスタの製造方法とした。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

21 - 40 / 172

[ Back to top ]