Fターム[5F110HM07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | チャネル領域と結晶構造が異なるもの (172)

Fターム[5F110HM07]に分類される特許

101 - 120 / 172

MOSFETデバイスにおける浮遊体効果を減少させる方法及び構造体

【課題】 シリコン・オン・インシュレータ(SOI)デバイスを含む金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおける浮遊体効果を減少させる方法及び構造体を提供すること。

【解決手段】 電界効果トランジスタ(FET)デバイスは、バルク基板と、バルク基板の上に形成されたゲート絶縁層と、バルク基板に関連する活性デバイス領域内に形成されたソース及びドレイン領域であって、各々が活性デバイス領域のボディ領域に対するp/n接合部を画定するソース及びドレイン領域と、ソース領域内に画定され、ソース領域のp/n接合部を横切ってボディ領域内に至るキャビティの内部に形成された導電性プラグとを含み、ここで導電性プラグはボディ領域とソース領域の間の放電経路を促進する。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】良好なコンタクト抵抗を有し良好な電気的特性を備える薄膜半導体装置及びその製造方法を提供する。

【解決手段】ガラス基板、樹脂基板等を用いた基板11上にSixGe1−xからなる半導体層13を形成する。半導体層13の表面領域に第1ソース領域14と第1ドレイン領域16とを形成した上で、この領域を覆うようにニッケル薄膜を形成し、500℃以下で熱処理を施す。続いて、未反応のニッケル薄膜をエッチングによって除去することによって、第1ソース領域14と第1ドレイン領域16に対して自己整合的にソースコンタクト層18とドレインコンタクト層19とを形成することができる。

(もっと読む)

引張歪みおよび圧縮歪みを生成するための埋め込みSi/Ge材料を含むNMOSトランジスタおよびPMOSトランジスタを有する半導体デバイス

1つの能動領域(105A,205A,305A,405A)に、実質的に連続し、かつ均一な半導体合金(107,207,307,407)を形成する一方で、第2能動領域(105B,205B,305B,405B)の中央部分にベースの半導体材料(113B,213B,313B、401)を提供するために、そこに半導体合金(107,207,307,407)をパターニングすることにより、異種の歪みが誘発されうる。一方、前記ベースの半導体材料(113A,213A,313A,413A)に対応するカバー層を提供した後に、前記ゲート誘電体(122,322,422)を形成するための確立されたプロセス技術が使用されうる。一部の例示的な実施形態では、実質的な自己整合プロセスが提供される。このプロセスでは、前記層(208,308)を基に前記ゲート電極(121,221,321,421)が形成され、前記層(208,308)は、前記能動領域(205B、305B)の一方の前記ベースの半導体材料の前記中央部分(213B、313B)を画定するためも使用されうる。このため、単一の半導体合金(107,207,307,407)を使用することにより、異なる導電型のトランジスタ(120A,120B)の性能が個別に改善されうる。  (もっと読む)

(もっと読む)

カルコゲナイド層を持つ薄膜トランジスタ及びその製造方法

【課題】カルコゲナイド層を有する薄膜トランジスタ及びその製造方法を提供する。

【解決手段】チャンネル層を構成する非晶質のカルコゲナイド層と、非晶質のカルコゲナイド層の両側部にそれぞれ形成されてソース及びドレイン領域を構成する結晶質のカルコゲナイド層と、結晶質のカルコゲナイド層に連結されたソース電極及びドレイン電極と、非晶質のカルコゲナイド層の上部または下部に、ゲート絶縁層を介在して形成されたゲート電極とを備える薄膜トランジスタである。これにより、カルコゲナイド層を光伝導層として利用して光薄膜トランジスタを具現したり、非晶質のカルコゲナイド層と結晶質のカルコゲナイド層とによって、ダイオード整流機能を具備する電気薄膜トランジスタを具現できる。

(もっと読む)

半導体装置

【課題】電子供給層と絶縁層との間の界面準位を低減させ、リーク電流やドレイン電流のコラプス等の抑制を可能とすること。

【解決手段】本発明は、基板(10)上に設けられたGaN電子走行層(12)と、電子走行層(12)上に設けられ2次元電子ガス(13)を電子走行層(12)に生成するAlGaN電子供給層(14)と、電子供給層(14)上に設けられたGaN層(20)と、GaN層(20)との間に絶縁膜(32)を介し設けられたゲート電極(34)と、を具備する半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法の1形態として、多結晶半導体を用いて薄膜トランジスタ(TFT)を形成する工程で、TFT内部にあるチャネル領域に、異なる結晶粒径を有する構造を形成することは困難であった。そのため、チャネル領域に電流駆動能力の大きい結晶粒の大きいTFTを形成すると寄生バイポーラ効果により電気的な動作が不安定になる。又寄生バイポーラ効果を抑制可能な微細結晶を用いた場合には、電流駆動能力が小さくなるという課題がある。

【解決手段】チャネル部分に半透過マスクを用いたパターンを形成し、レーザーアニールを行う場合に、チャネル近傍でのアニール後の結晶粒の分布を制御する。例えばチャネル中央領域に強いレーザーアニールを行い、ゲート端部に弱いレーザーアニールを施すことで寄生バイポーラ動作の発生を抑制し、且つ高い電流駆動能力を持つ半導体装置としてのTFTの製造方法を提供することができる。

(もっと読む)

薄膜トランジスタおよびその製造方法ならびに表示装置

【課題】オン/オフ比が高く、キャリア移動度が改善された薄膜トランジスタおよびその製造方法ならびに表示装置を提供する。

【解決手段】基板2上に、ゲート電極3と、ゲート絶縁膜4と、チャネル層5と、ソース・ドレイン層7,8とをこの順またはこれと逆の順に積層してなる薄膜トランジスタにおいて、ソース・ドレイン層7,8は、n型微結晶シリコン層7a,8aとn型非晶質シリコン層7b,8bとで構成されており、チャネル層5側が微結晶シリコン層7a,8aとなるように配置されていることを特徴とする薄膜トランジスタおよびその製造方法ならびに表示装置である。

(もっと読む)

MIS型電界効果トランジスタおよびその製造方法

【課題】パワーデバイスへの適用に適したIII-V族窒化物半導体MIS型電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタは、サファイア基板1上に窒化物半導体積層構造部2を配置して構成されている。窒化物半導体積層構造部2は、N型GaN層5、このN型GaN層5に積層されたP型GaN層6、およびこのP型GaN層6に積層されたN型GaN層7を有している。窒化物化合物半導体積層構造部2には、断面V字形のトレンチ16が形成されており、このトレンチ16の側壁は、N型GaN層5、P型GaN層6およびN型GaN層7に跨る壁面17を形成している。この壁面17にゲート絶縁膜が形成され、さらに、このゲート絶縁膜19を挟んで壁面17に対向するようにゲート電極20が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】電極の接触抵抗、電極自身の抵抗の低減によって高性能化した電界効果トランジスタを含む半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板200に形成されたチャネル領域106と、ゲート絶縁膜101を介して形成されたゲート電極と、チャネル領域106の両側に形成されたソース電極およびドレイン電極を具備するn型電界効果トランジスタを含み、ソース電極およびドレイン電極が第1の金属のシリサイド110aで形成され、半導体基板200と第1の金属のシリサイド110aとの界面に、第2の金属120aを含有する界面層が形成され、第2の金属120aの仕事関数が第1の金属のシリサイド110aの仕事関数よりも小さく、かつ、第2の金属120aのシリサイドの仕事関数が第1の金属のシリサイド110aの仕事関数よりも小さいことを特徴とする半導体装置およびその製造方法。

(もっと読む)

MIS型電界効果トランジスタおよびその製造方法

【課題】パワーデバイスへの適用に適したIII-V族窒化物半導体MIS型電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタは、サファイア基板41上に窒化物半導体積層構造部2を配置して構成されている。窒化物半導体積層構造部2は、超格子N型層5、この超格子N型層5に積層されたP型GaN層6、およびこのP型GaN層6に積層された超格子N型層7を有している。窒化物化合物半導体積層構造部2には、断面V字形のトレンチ16が形成されており、このトレンチ16の側壁は、超格子N型層5、P型GaN層6および超格子N型層7に跨る壁面17を形成している。この壁面17にゲート絶縁膜が形成され、さらに、このゲート絶縁膜19を挟んで壁面17に対向するようにゲート電極20が形成されている。

(もっと読む)

パフォーマンス強化材料組成を含む歪みチャネル領域を有するトランジスタ

ゲートのパターニングの前にシリコンベースの活性半導体領域中に半導体合金(107、107A、107B、207A、207B、307)を形成することによって、その歪み誘発効果に加えて半導体合金自体の材料特性も利用することができる。したがって、高度な電界効果トランジスタのデバイスパフォーマンスであっても、ドレインおよびソース領域中に歪み半導体合金を用いることで従来のアプローチ法よりも向上させることができる。  (もっと読む)

(もっと読む)

応力がかけられたチャネル領域を有する改善されたCMOSデバイス及びそれを製造する方法(半導体デバイスおよび該半導体デバイスの形成方法)

【課題】 同じ応力誘起材料を用いて、n−FET及びp−FET内に異なる応力(すなわち、圧縮及び引張)を生成し、それぞれ内部の電子移動度及び正孔移動度を増大させること。

【解決手段】 本発明は、応力がかけられたチャネル領域を有する改善された相補型金属酸化膜半導体(CMOS)デバイスに関する。具体的には、各々の改善されたCMOSデバイスが、半導体デバイス構造体内に配置されたチャネル領域を有する電界効果トランジスタ(FET)を含み、半導体デバイス構造体は、第1の組の等価な結晶面の1つに沿って配向された上面と、第2の異なる組の等価な結晶面に沿って配向された1つ又は複数の付加的な表面とを有する。こうした付加的な表面は、結晶学的エッチングによって容易に形成することができる。さらに、内因性圧縮応力又は引張応力を有する1つ又は複数のストレッサ層が、半導体デバイス構造体の付加的な表面の上に配置され、かつ、FETのチャネル領域に引張応力又は圧縮応力をかけるように配置され、構成される。こうしたストレッサ層は、半導体デバイス構造体とは異なる格子定数を有する半導体材料の擬似格子整合成長によって形成することができる。

(もっと読む)

半導体構造体およびその形式、方法(多層埋込みストレッサを形成するための構造および方法)

【課題】デバイス・チャネル領域に歪みを誘起する半導体構造体で使用される、段階的ドーパント分布構造を有する多層埋込みストレッサを提供する。

【解決手段】本発明の多層ストレッサは、ソース/ドレイン領域が一般に位置決めされる半導体構造体の部分内に形成される。本発明の多層ストレッサは、アンドープか低濃度にドープされた第1の共形エピ半導体層と、第1のエピ半導体層に比べて高濃度にドープされた第2のエピ半導体層とを含む。第1および第2のエピ半導体層各々は、同じ格子定数を有し、この格子定数は、それらの半導体層が埋め込まれた基板の格子定数と異なっている。本発明の多層埋込みストレッサを含む構造は、応力近接と短チャネル効果の良好なバランスを実現し、さらに深いソース/ドレイン領域の形成中に一般に生じるどんな可能な欠陥もなくするか、実質的に減少させる。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタおよび表示装置

【課題】薄膜トランジスタの特性を劣化させずにその特性ばらつきを抑えることが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】結晶質シリコン膜13Pを、光熱変換層15およびバッファ層14を介した間接的な加熱処理によって形成する。バッファ層14および絶縁膜16のパターニングによって、結晶質シリコン膜13P上のチャネル領域に対応する領域にチャネル保護膜を選択的に形成する。また、n+シリコン膜17および金属膜18を選択的に除去する際に、チャネル保護膜をエッチングストッパとして機能させる。結晶質シリコン膜13Pの形成の際に、均一に熱が供給される。また、エッチングの際に、結晶質シリコン膜13Pのチャネル領域が保護される。

(もっと読む)

画像表示システム及び低温ポリシリコンのレーザアニール方法

【課題】結晶粒径を拡大し、薄膜トランジスタの電子移動度を高める画像表示システム及び低温ポリシリコンのレーザアニール方法を提供する。

【解決手段】本発明に係る低温ポリシリコンのレーザアニール方法は、i)第1金属層22とシリコン膜層23とが形成されたガラス基板21に用いられ、波長が400nm以上のレーザ光Lをシリコン膜層23に照射し、シリコン膜層23がレーザ光の一部成分を吸収して溶融され、且つレーザ光の他の成分がシリコン膜層23を透過し第1金属層22からシリコン膜層23に反射され、シリコン膜層23が反射されたレーザ光の他の成分を吸収し、溶融され再結晶化されるステップと、ii)レーザ光を照射した後、シリコン膜層23を静置することにより、シリコン膜層23の温度を室温まで下げるステップと、を含む。

(もっと読む)

insituまたはexsitu熱処理と組み合わされた改良型電界効果トランジスタ向けのイオン注入(FETデバイスを製造する方法およびFETデバイス)

【課題】所望のドーパント密度プロファイルを達成することができ、アモルファス化される層の厚さが十分に限定され、または歪み緩和のレベルが十分に低く、あるいはこれらがともに達成されるイオン注入法を提供することにある。

【解決手段】本発明は、イオン注入ステップをin situまたはex situ熱処理と組み合わせて、注入誘起性のアモルファス化(超薄シリコン・オン・インシュレータ層のFETのソース/ドレイン(S/D)領域の潜在的な問題)、および歪まされたS/D領域の注入誘起性の塑性緩和(その下の基板層と格子不整合の状態にある埋込みS/D領域によってチャネル歪みが誘起される歪みチャネルFETの潜在的な問題)をともに回避し、またはともに最小化し、あるいは一方を回避し、もう一方を最小化する方法を教示する。第1の実施形態では、イオン注入を高温で実行することによって、イオン注入がin situ熱処理と組み合わされる。第2の実施形態では、熱注入を実行する能力を有する手段を必要としない「デバイデッド−ドーズ−アニール−イン−ビトウィーン」(DDAB)法において、イオン注入がex situ熱処理と組み合わせられる。

(もっと読む)

半導体装置およびその製造方法

【課題】 十分なキャリア移動度を有するチャネル部を備えた半導体装置およびその製造方法を提供する。

【解決手段】 基板14の絶縁層12上に形成された突起状の第1導電型の第1半導体層13と、第1半導体層13の第1側面および第1側面と対向する第2側面上にゲート絶縁膜16a、16bを介して形成されたゲート電極17と、第1半導体層13の第3側面に、基板14の絶縁層12上から形成された第1半導体層13と異なる第2導電型の第2半導体層18a、18bを有するソース領域19と、第1半導体層13の第3側面と対向する第4側面に、基板14の絶縁層12上から形成された第1半導体層13と異なる第2導電型の第2半導体層18c、18dを有するドレイン領域20とを具備する。

(もっと読む)

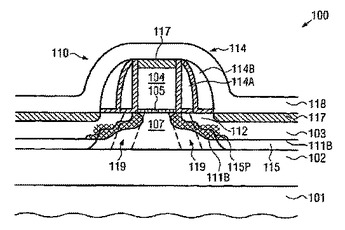

ボディポテンシャルが低減したSOIトランジスタとその製造法

炭素、フッ素などの原子種(111B)をドレイン及びソース領域(115、206)とボディ領域(107、207)とに導入することで、SOIトランジスタ(110、210M)の接合部のリークが著しく増加し、これにより、蓄積した少数電荷キャリアに対してリークパス(119、219A)が強化される。これにより、ボディポテンシャルの変動が著しく減り、その結果、最新のSOIデバイス(100)の全体のパフォーマンスが向上する。具体的な実施形態では、このメカニズムは、スタティックRAM領域(250M)などのしきい値電圧にセンシティブなデバイス領域に選択的に適用することができる。  (もっと読む)

(もっと読む)

ドレイン及びソース領域にリセスを設けることでチャネル領域に極めて近接するトランジスタにストレスソース与える技術

電界効果トランジスタ(100、200)の隣接するチャネル領域(104、204)中の歪みの生成が向上するように、ドレインならびにソース領域(114、214)にリセス(112D、212D)を設けることによって、コンタクトエッチストップ層などの高応力層(118、218)がリセス(112、212)に形成される。さらに、金属シリサイド(217)の望ましくない緩和効果を低減するか回避することによって、歪みのある半導体材料(230)がチャネル領域(104、204)に非常に近接して設けられることから、歪みを生成する実効性もまた向上する。ある態様では、さらに実効的な歪み生成メカニズムを得るように、両方の効果を組み合わせてもよい。  (もっと読む)

(もっと読む)

静電的に制御されるトンネリング・トランジスタ

【課題】2つのトンネル接合の間に配設されたアイランドの静電電位を変化させることにより動作するトランジスタ。

【解決手段】本トランジスタは、バンド・ギャップを有するアイランド26、ソース・コンタクト28及びドレイン・コンタクト30が設けられ、アイランド26とドレイン30間に第1のトンネル接合障壁36を有する。アイランドは、トランジスタの他の部分及び基板からオーム的に分離される。ゲート電圧によりアイランドの電位が変化するように、ゲート電極24がアイランド26に容量結合される。本トランジスタはn型及びp型実施形態を有する。動作時、正のゲート電圧を印加するとアイランドの伝導帯が降下し、負のゲート電圧印加で価電子帯が上昇する。伝導帯又は価電子帯がソース及びドレインのフェルミ準位と整合している時、トンネル効果電流がソース、アイランド及びドレインの間を通ることができる。

(もっと読む)

101 - 120 / 172

[ Back to top ]