Fターム[5F110HM07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | チャネル領域と結晶構造が異なるもの (172)

Fターム[5F110HM07]に分類される特許

81 - 100 / 172

半導体装置の製造方法、半導体装置および半導体層の形成方法

【課題】半導体上にモフォロジの良好な半導体層を選択的にエピタキシャル成長させる。

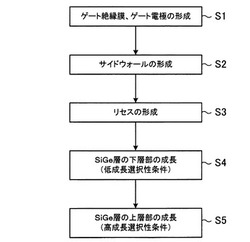

【解決手段】リセスド・ソース・ドレイン型pMOSFETを形成する際、STIを形成したSi基板上にゲート絶縁膜を介してゲート電極を形成し(ステップS1)、サイドウォールを形成した後(ステップS2)、その両側のSi基板に部分的にリセスを形成する(ステップS3)。そして、そのSi基板のリセス内に、下層部の方が上層部よりも、サイドウォールやSTIに対する成長選択性が低くなるような条件を用いて、下層部と上層部をエピタキシャル成長させ、SiGe層を形成する(ステップS4,S5)。これにより、Si基板のリセス内に、サイドウォール等に対する成長選択性を確保しつつ、モフォロジの劣化が抑えられたSiGe層を形成することが可能になる。

(もっと読む)

半導体装置とその製造方法

【課題】 オン抵抗とゲート閾値電圧の間に存在するトレードオフ関係を打破すること。

【解決手段】 半導体装置10は、半導体下層22と、第1不純物拡散抑制膜24aと、第3不純物拡散抑制膜24cと、半導体上層26と、第1不純物拡散抑制膜24a上の半導体上層26の一部に設けられているドレイン領域31と、第3不純物拡散抑制膜24c上の半導体上層26の一部に設けられているソース領域35と、ドレイン領域31とソース領域35の間の半導体上層26に対向するゲート電極34を備えている。半導体上層26内のp型不純物の濃度は、第1不純物拡散抑制膜24a及び第3不純物拡散抑制膜24c上で薄く、半導体下層22の第2領域22b上で濃い。

(もっと読む)

半導体装置およびその製造方法

【課題】傾斜型積み上げソース/ドレイン構造のMISトランジスタを高速化する。

【解決手段】MISトランジスタは、基板1上のゲート電極4と、基板1上にゲート電極4の側壁に沿う側壁絶縁膜6aと、基板1の主面に一端がゲート電極4の側壁下のソース/ドレイン半導体領域3と、ソース/ドレイン半導体領域3上に第1の側壁絶縁膜6aに接する積み上げ層5aと、積み上げ層5a上に側壁絶縁膜6aに沿う側壁絶縁膜6bと、積み上げ層5a上に側壁絶縁膜6bに接する積み上げ層5bと、を備える。

(もっと読む)

半導体装置、その製造方法、及び表示装置

【課題】開口率を向上させることができる半導体装置を提供すること。

【解決手段】本発明に係る半導体装置は、基板上の所望の位置に形成される遮光層41と、遮光層41及び基板20上に形成される下地膜21と、下地膜21上に形成され、ソース領域及びドレイン領域並びにチャネル領域を有する第1の半導体領域31及び第2の半導体領域42と、第1の半導体領域31及び第2の半導体領域42上に形成されたゲート絶縁膜22と、ゲート絶縁膜22上に、第1の半導体領域31及び第2の半導体領域42と対向する位置にそれぞれ形成されたゲート電極を備え、第1の半導体領域42のチャネル領域は遮光層41と対向する位置に形成され、非晶質半導体からなり、第2の半導体領域31のチャネル領域は多結晶半導体からなる。

(もっと読む)

フリンジ電界の電荷注入のための電極構造

【課題】電子機器の半導体材料に改良された電荷注入を備える新規電極構造を提供する。

【解決手段】半導体デバイスは、半導体材料及び半導体材料に電気的に接続された電極構造を備える。電極構造は、第1の導体材料で形成された第1の部分及び第2の導体材料で形成された第2の部分を有する。電極構造の第1の部分及び第2の部分の両方は、半導体材料と直接的に接触している。第1の導体材料は、第1の仕事関数を有し、第2の導体材料は、第1の仕事関数と異なる第2の仕事関数を有する。電極構造の第2の部分は、第1の部分と共に接合部点を形成する。電極構造の第1の部分及び第2の部分は、第1の導体材料と第2の半導体材料との間の接合部の端部からフリンジ電界が半導体材料中へ広がるように配置される。

(もっと読む)

歪みが強化された半導体デバイスとその製造方法

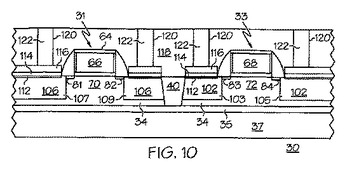

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 基板の歪を生ずることなく、不純物領域の不純物の活性化率を向上させ、優れた特性の薄膜半導体装置を製造することを可能とする薄膜半導体装置の製造方法を提供すること。

【解決手段】 絶縁性基板上に非単結晶半導体層を形成する工程と、前記非単結晶半導体層にレーザー光を照射して結晶化領域を形成する工程と、前記結晶化領域上にゲート絶縁膜及びゲート電極を形成する工程と、前記結晶化領域の所定の位置の上層部を非結晶化するプリアモルファス化工程と、前記結晶化領域の所定の位置に不純物をドーピングする工程と、熱処理により前記結晶化領域の所定の位置にソース領域及びドレイン領域を形成する工程とを具備することを特徴とする。

(もっと読む)

窒化物化合物半導体素子およびその製造方法

【課題】酸化膜或いは絶縁膜が部分的に薄くなることによる耐圧の劣化や、その厚さが過剰になることによる直流利得gmの低下を防ぐことができる高性能な窒化物化合物半導体素子およびその製造方法を提供する。

【解決手段】ソース電極,ドレイン電極とそれぞれオーミック接触するn+コンタクト領域8,9、および電界集中の緩和を目的としたリサーフ層(リサーフ領域)と呼ばれるn-領域10を、それぞれ選択成長法によって形成する。選択成長法によるn+コンタクト領域8,9およびn-領域10の形成後に、選択成長によってn+コンタクト領域8,9およびn-領域10にそれぞれ生じた凸部8a,9aおよび10aを化学機械研磨(CMP)法により平坦する。

(もっと読む)

縦型スピントランジスタ及びその製造方法

【課題】トランジスタ及びその製造方法に関して、新たな構造のスピントランジスタ及びその製造方法を提案すること。

【解決手段】磁性体で形成された層を含んでいる第1のソースドレイン層と;前記第1のソースドレイン層上に形成されており、半導体で形成された層を含んでいる、チャネル層と、前記チャネル層上に形成されており、磁性体で形成された層を含んでいる、第2のソースドレイン層と、を含む突起構造と;前記チャネル層の側面に形成されたゲート絶縁膜と;前記ゲート絶縁膜の表面に形成されたゲート電極と;を具備することを特徴とする縦型スピントランジスタ。

(もっと読む)

ソース/ドレイン・ストレッサーおよびそのための方法

半導体デバイス(10)を形成する方法を提供する。該方法は基板(12)の上に横たわるゲート構造体(22)を形成することを含む。方法は更にゲート構造体(22)に隣接する側壁スペーサ(24)を形成することを含む。方法は更に、半導体デバイス(10)のソース側の方向に角度がついたインプラント(26)を実行することを含む。方法は更に半導体デバイス(10)をアニーリングすることを含む。方法は更に基板の側壁スペーサ(24)対向する端に隣接するレセス(32,34)を形成し、1の型の半導体材料(16)を露出させることを含む。方法は更にレセスに第2の型の半導体材料(36,38)をエピタキシャル成長させることを含み、第2の型の半導体材料が第1の型の半導体材料の格子定数とは異なる格子定数を有し、半導体デバイス(10)のチャネル領域に応力を形成することを含む。 (もっと読む)

GaN系半導体素子の製造方法

【課題】ソース電極やドレイン電極のアニール処理を行っても、ゲート領域の半導体層界面が劣化しないGaN系半導体素子の製造方法を提供する。

【解決手段】 サファイア基板1上にアンドープGaN層2、n型AlGaNドレイン層3、n型GaN層4、p型GaNチャネル層5、n型GaNソース層6が形成されている。n型AlGaNドレイン層3〜n型GaNソース層6に至る積層構造を、断面がほぼ矩形となるようにn型GaN層ソース層6からn型AlGaNドレイン層3が露出する深さまでエッチングして、ドレイン電極8とソース電極7とを作製し、電極アニール処理を行う。その後、ゲートを形成するためのエッチングを行い、ゲート絶縁膜9、ゲート電極10を形成する。

(もっと読む)

半導体装置

【課題】チャネル長の長いトランジスタの高速駆動を実現するとともに、チャネル長の短いトランジスタにおける特性の変動を抑制した半導体装置を提供する。

【解決手段】本発明による半導体装置(100)は、第1多結晶領域(P1)を有する第1半導体層(112)と、第1ゲート電極(114)とを含む第1トランジスタ(110)と、第2多結晶領域(P2)を有する第2半導体層(122)と、第2ゲート電極(124)とを含む第2トランジスタ(120)とを備える。第2チャネル領域(C2)のチャネル長は第1チャネル領域(C1)のチャネル長よりも短く、第2多結晶領域(P2)の平均結晶粒径は第1多結晶領域(P1)の平均結晶粒径よりも小さい。

(もっと読む)

マルチレイヤ・ソース/ドレイン・ストレッサー

半導体デバイスのドレイン領域にレセス(28)と、ソース領域にレセス(26)とを包含する半導体デバイスを形成する方法。該方法は更に、ソース領域のレセス(26)に第1の半導体材料層(32)と、ドレイン領域のレセス(28)に第2の半導体材料層(34)とを形成することを有し、第1の半導体材料層(32)と第2の半導体材料層(34)の各々が、第1の元素の原子濃度と第2の元素の原子濃度との第1の比を備えたストレッサー材料を用いて形成され、第1の元素が、ドーピング材料の第1の濃度レベルを備えたシリコンであることを特徴とする。該方法は更に、第1の半導体材料層(32)の上に横たわる追加の半導体材料層(36,38,40,42)と、第1の元素の原子濃度と第2の元素の原子濃度との異なる比率を備えた第2の半導体材料層(34)とを有する。  (もっと読む)

(もっと読む)

GaN系半導体素子

【課題】高耐圧、低リークのGaN系半導体積層構造を有するGaN系半導体素子を提供する。

【解決手段】基板1の上に第3n型GaN系半導体層3、第1n型GaN系半導体層4、i型GaN系半導体層5、p型GaN系半導体層6、第2n型GaN系半導体層7が積層された積層構造で表される。p型GaN系半導体層6の不純物濃度は、1×1020 cm−3以下であり、第1n型GaN系半導体層4の不純物濃度は1×1018cm−3以下に構成される。

(もっと読む)

トランジスタにシリコン/ゲルマニウム(Si/Ge)含有ドレイン/ソース領域をシリコン/ゲルマニウム損失を削減して形成する方法

高ゲルマニウム濃度のシリコン/ゲルマニウム材料上に保護層を設けることで、対応する歪み半導体材料の損失が著しく低減するか、損失を完全に回避することもできる。保護層は、重要な洗浄プロセスの前に形成され、金属シリサイドを形成するまで保持される。よって、選択的エピタキシャル成長プロセスにおいて、広範囲にわたって、過剰に埋め込みを行う必要なく、p型トランジスタの高パフォーマンスゲインを実現することができる。  (もっと読む)

(もっと読む)

非合金化シリサイドを有する移動度が高められたMOSFETのための構造体及び方法

【課題】 埋設シリコン・ゲルマニウム合金及びシリコン炭素合金は、特に応力エンジニアリングによってMOSFETの移動度を向上させるために、多くの有用な用途を提供するが、これらの表面上の合金化シリサイドの形成はデバイス性能を低下させる。

【解決手段】 本発明は、半導体基板上に配置されたそのようなシリコン合金表面上に非合金化シリサイドを設けるための構造体及び方法を提供する。これにより、同じ半導体基板上の埋設SiGeによって移動度が高められたPFET及び埋設Si:Cによって移動度が高められたNFETの両方に対して、低抵抗コンタクトの形成が可能になる。さらに、本発明は、トランジスタ・デバイスのチャネル上の応力を増大させるために、ゲート誘電体のレベルを上回る厚いエピタキシャル・シリコン合金、特に厚いエピタキシャルSi:C合金についての方法を提供する。

(もっと読む)

電界効果トランジスタ素子およびその製造方法

【課題】改善した能力を備えた、MOSFETやHEMTなどの半導体トランジスタ素子を提供する。

【解決手段】本発明に係る半導体トランジスタ素子は、トランジスタがオンしたとき、電流をトランジスタに通すために、キャリアが移動できるチャネル層を含むチャネルエリア(1)と、チャネル層に対して電流を供給するために、チャネル層と接触したソースエリア(4)およびドレインエリア(5)と、ゲート電極(3)とを備え、好ましくは、ゲート電極とチャネル層との間にゲート誘電体(2)が設けられ、前記チャネル層はIII−V族材料からなり、前記ソースエリアおよびドレインエリアはSiGe(SixGe1−x、xは0と100%の間)を含み、ヘテロ接合(30,31)がIII−V族材料とSiGeの間に存在し、前記ヘテロ接合は、前記電流が前記ヘテロ接合を通過するように配置されており、前記ヘテロ接合(30,31)は、前記ゲート誘電体(2)または前記ゲート電極と交差するように配向している。

(もっと読む)

半導体装置の製造方法

【課題】薄いチャネルを有する薄膜トランジスタを形成する。

【解決手段】絶縁層6上にソース・ドレイン材料膜12を形成した後、絶縁層6に達する開口部13をソース・ドレイン材料膜12に形成する。次いで、開口部13内の絶縁層6およびソース・ドレイン材料膜12上に、所望の膜厚のチャネル4およびゲート絶縁膜5を順に形成した後、ゲート絶縁膜5上であって開口部13内を埋め込むゲート材料膜14を形成する。次いで、ゲート材料膜14上にキャップ膜7を形成し、ゲート材料膜14からなるゲート1を形成する。次いで、ソース・ドレイン材料膜12上にマスク層を形成する。次いで、ゲート1をキャップ膜7で保護しながらマスク層で保護されていないソース・ドレイン材料膜12を除去し、ゲート1の両側にソース・ドレイン材料膜12を残す。一方のソース・ドレイン材料膜12がソース2、他方の前記ソース・ドレイン材料膜12がドレイン3となる。

(もっと読む)

応力増強トランジスタおよびその作製方法

応力増強MOSトランジスタ(30)およびその作製方法を提供する。第1の表面(37)を有する半導体層(38)を含むセミコンダクタ・オン・インシュレータ構造(36)が提供される。歪み誘起エピタキシャル層(50)が、前記第1の表面(37)上にわたってブランケット堆積され、次いで、前記第1の表面(37)上を覆うソース領域(51)およびドレイン領域(52)を作成するために使用されうる。  (もっと読む)

(もっと読む)

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】 リンでドープされたシリコンと炭素を含有するエピタキシャル層を形成する方法を提供する。

【解決手段】 圧力は、堆積中100トール以上に維持される。方法は、置換型炭素を含む膜の形成を生じさせる。特定の実施形態は、半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおけるエピタキシャル層の形成と処理に関する。

(もっと読む)

81 - 100 / 172

[ Back to top ]