Fターム[5F110HM07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | チャネル領域と結晶構造が異なるもの (172)

Fターム[5F110HM07]に分類される特許

161 - 172 / 172

移動度を半導体素子において増加させる方法及び装置

トランジスタのチャネル領域における移動度の増大を実現する方法及び装置が提示される。一の実施形態では、チャネル領域(18)は2軸応力が発生する基板の上に形成される。ソース領域(30)及びドレイン領域(32)は基板の上に形成される。ソース領域及びドレイン領域は1軸応力を2軸応力発生チャネル領域に追加する形で発生させるように作用する。1軸応力及び2軸応力はPチャネルトランジスタに関しては共に圧縮応力であり、そしてNチャネルトランジスタに関しては共に引っ張り応力である。その結果、キャリア移動度が短チャネルトランジスタ及び長チャネルトランジスタの両方に関して増加する。両方のタイプのトランジスタを同じ集積回路に搭載することができる。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】PMOSFETにおいて、ショートチャネル効果を抑制でき、より短いゲート長での動作を確保できる半導体装置及びその製造方法を提供することである。

【解決手段】半導体基板に形成されたnウエル領域とnウェル領域上に形成されたゲート電極と、ゲート電極の両端部のnウェルの表面層に形成された一対のボロン含有拡散領域と、ボロン含有拡散領域と同等もしくはより深く、かつ、ゲート電極下においてボロン含有拡散領域と同等もしくはより広い、フッ素、窒素、または炭素からなる群から選択される少なくともいずれかの一の拡散抑制元素を拡散した拡散抑制元素拡散領域と、ボロン含有拡散領域より深く、かつ、横方向端部がボロン含有拡散領域の横方向端部よりゲート電極端から離れた位置にあるp型の不純物拡散領域とを有する半導体装置である。

(もっと読む)

半導体素子及びその製造方法

【課題】素子の電流駆動力を向上させ、ショットチャンネル効果を改善させることができる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、Si−エピ層20,120を食刻して下部の埋込絶縁膜50,200を露出させ、一側のLDD40,180領域から他側のLDD領域40,180まで互いに平行して延長される開口部140を1つ以上形成し、ゲート電極がSi−エピ層20,120の表面を取り囲むようにした。

(もっと読む)

電子回路装置、画素表示装置及び電子回路装置の製造方法

【課題】画素駆動回路を構成する薄膜トランジスタのキャリアの移動速度の増大と、1画素用駆動回路内の薄膜トランジスタの閾値電圧Vthのばらつきの抑制とを図る画素駆動回路を含む電子回路装置、画素表示装置及び前記電子回路の製造方法を提供すること。

【解決手段】絶縁基板上に設けられた非単結晶半導体膜と、この非単結晶半導体膜に設けられた複数個の結晶化半導体領域(54)と、この各結晶化半導体領域内に少なくともチャネル領域(Ch1,CH2,Ch3,Ch4)が設けられた複数個の薄膜トランジスタとを具備し、少なくとも1個の薄膜トランジスタのソース領域および/又はドレイン領域(S1,S2,D3,D4)の一部は結晶化半導体領域(54)からはみ出して配置されている。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体層のソース/ドレイン領域の全部または一部分とキャパシターの第1電極をMIC結晶化法で結晶化して、半導体層のチャネル領域全部をMILC結晶化法で結晶化された薄膜トランジスタ及びキャパシターの半導体素子及びその製造方法を提供する。

【解決手段】その製造方法は、薄膜トランジスタの半導体層とキャパシターの第1電極を非晶質シリコンで形成した後、MICおよびMILC結晶化法で結晶化して、薄膜トランジスタのゲート電極及びキャパシターの第2電極を同じ物質で形成することによって簡単な工程で薄膜トランジスタとキャパシターを同時に形成することができるだけでなく、各素子に適合な結晶化法で結晶化することによって、低い温度及び短い時間に結晶化を進行して基板が収縮したり曲がる現象が発生しないだけでなく、薄膜トランジスタの半導体層の特性とキャパシターの特性が優秀であるという効果がある。

(もっと読む)

薄膜トランジスター及びその製造方法

【課題】 ジャンクション領域にシード又は結晶粒境界が形成されないように、キャッピング層をパターニングして結晶化することにより、薄膜トランジスターの素子特性を向上させて均一な値を得ることができる薄膜トランジスター及びその製造方法を提供する。

【解決手段】 本発明による薄膜トランジスターの製造方法は、基板上に非晶質シリコン層を形成する段階と、前記非晶質シリコン層を結晶化してパターニングして半導体層パターンを形成段階と、前記半導体層パターン上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上にゲート電極を形成する段階と、を含み、前記半導体層パターン内にはシード又は結晶粒境界が存在するが、ジャンクション領域にはシード又は結晶粒境界が存在しないことを特徴とする。

(もっと読む)

セミコンダクタ・オン・インシュレータ半導体装置及び製造方法

セミコンダクタ・オン・インシュレータ半導体装置は金属又はシリサイド・ソース・コンタクト領域及びドレイン・コンタクト領域(38、40)、活性化ソース領域及びドレイン領域(30、32)並びに本体領域(34)を有する。構造体は二重ゲートSOI構造体又は完全空乏型(FD)SOI構造体でよい。スペーサ(28)を使用し、半導体層の全厚みをコンタクト領域で完全に置き換えるプロセスを用いてシャープな海面と低抵抗とが達成される。  (もっと読む)

(もっと読む)

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ。

前記電界効果トランジスタは、ゲート絶縁膜(3)によりチャネル(7)から分離されたゲート電極(5)により制御されるチャネル(7)により接続されるソース(10)及びドレイン(11)を含む。前記チャネル(7)はダイアモンド状のカーボン層により形成される。前記トランジスタの製造方法は、続いて、ダイアモンド状のカーボン層を基板上(2)に堆積させ、ゲート絶縁層(3)を堆積させ、そして、少なくとも1つの導電層(4)を堆積させることを含む。前記導電層(4)は前記ゲート電極(5)からエッチングされる。次に、側面の絶縁膜(6)を形成するために、前記ゲート電極(5)の側面に絶縁材料が堆積される。次に、前記ゲート絶縁層(3)がエッチングされ、そして、前記ダイアモンド状のカーボン層がチャネル(7)の輪郭を描くようにエッチングされる。次に、前記ソース(10)を形成するための半導体材料、及び前記ドレイン(11)を形成するための半導体材料がチャネル(7)の両側に堆積される。  (もっと読む)

(もっと読む)

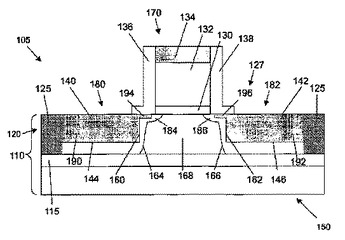

半導体装置及び半導体装置の製造方法

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

ローカルSOIを備えた半導体装置を形成するための方法

半導体・オン・インシュレータ・トランジスタ45が、バルクのシリコン基板12から形成される。活性領域は基板12上に画定され、単結晶である酸素リッチ型シリコン層は活性領域の頂部面に形成される。この酸素リッチ型シリコン層の上に、シリコンのエピタキシャル層が成長する。シリコンのエピタキシャル層が形成された後に、酸素リッチ型シリコン層が、該エピタキシャル層の少なくとも一部を単結晶シリコンとして残した状態にてシリコン酸化物24に変換される。これは、高温水蒸気をエピタキシャル層に適用することにより実施される。得られたものがトランジスタ45を形成するのに有用なシリコン・オン・インシュレータ構造体10であり、該トランジスタにおいて、ゲート誘電体26が残りの単結晶シリコン上に存在し、該ゲート28はゲート誘電体26上に存在し、かつ、ゲート28の下側にある残りの単結晶シリコン内にチャネル36が存在する。  (もっと読む)

(もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

161 - 172 / 172

[ Back to top ]