Fターム[5F110HM07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | チャネル領域と結晶構造が異なるもの (172)

Fターム[5F110HM07]に分類される特許

41 - 60 / 172

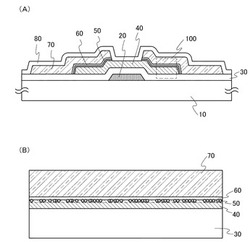

薄膜トランジスタ

【課題】電気特性が良好な、酸化物半導体を用いた薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極およびゲート絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられた金属酸化物膜と、金属酸化物膜上に設けられた金属膜と、を有し、酸化物半導体膜は、金属酸化物膜と接し、且つ、酸化物半導体膜の他の領域よりも金属濃度が高い領域(金属高濃度領域)を有する。金属高濃度領域には、酸化物半導体膜に含まれる金属が、結晶粒または微結晶として存在していてもよい。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

薄膜トランジスタ、有機電界発光表示装置、薄膜トランジスタの製造方法及び有機電界発光表示装置の製造方法

【課題】半導体層における特性が更に向上した薄膜トランジスタ及び当該薄膜トランジスタを備える有機電界発光表示装置とこれらの製造方法を提供すること。

【解決手段】本発明に係る薄膜トランジスタは、基板上に位置するバッファ層と、前記バッファ層上に位置するソース/ドレイン領域及び1又は複数のチャンネル領域を有する半導体層と、前記基板全面にわたって設けられるゲート絶縁膜と、前記ゲート絶縁膜上に設けられるゲート電極と、前記基板全面にわたって設けられる層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層と電気的に接触するソース/ドレイン電極とを含み、前記半導体層のチャンネル領域の多結晶シリコン層は、低角結晶粒界のみを含み、高角結晶粒界は、前記半導体層のチャンネル領域以外の領域に位置する。

(もっと読む)

埋め込み拡張領域を有するSOIトランジスタ、及びその形成方法

【課題】 改善された拡張部の抵抗及びチャネルの歪み特性を有するシリコン・オン・インシュレータ(SOI)トランジスタ及びそうしたSOIトランジスタを形成する方法を提供する。

【解決手段】 シリコン・オン・インシュレータ(SOI)トランジスタ・デバイスは、バルク基板の上に形成された埋め込み絶縁体層と、埋め込み絶縁体層上に形成されたSOI層と、トランジスタ・デバイスのソース及びドレイン領域に対応する、ゲート導体の対向する側に隣接して配置された一対のシリコン含有エピタキシャル領域とを含み、エピタキシャル領域の部分は、埋め込み絶縁体内に埋め込まれ、かつ、トランジスタ・デバイスのチャネル領域の対向する端部におけるソース及びドレイン拡張領域に対応するSOI層の垂直面及び底面の両方と接触している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置、この半導体装置の製造方法、前記半導体装置を備えた画素アレイ基板、前記半導体装置を備えたセンシング素子アレイ基板、表示パネル、インプットパネル、表示装置、携帯機器、X線検査装置、及びレントゲン装置

【課題】曲げストレスによるオン特性の劣化を抑制できる半導体装置、この半導体装置の製造方法、前記半導体装置を備えた画素アレイ基板、前記半導体装置を備えたセンシング素子アレイ基板、表示パネル、インプットパネル、表示装置、携帯機器、X線検査装置、及びレントゲン装置を提供する。

【解決手段】単結晶膜または多結晶膜からなる結晶化領域であるチャネル領域14と、アモルファス膜からなるアモルファス領域であるソース領域24及びドレイン領域34とからなる半導体層4を備えており、チャネル領域14は、半導体層4となるアモルファス膜を形成し、アモルファス膜に電流を流して一部分を結晶化することにより形成されてなる。

(もっと読む)

電界効果トランジスタ

【課題】高いしきい値電圧と大きい動作電流とを両立した電界効果トランジスタを提供すること。

【解決手段】基板と、前記基板上に形成され、窒化物系化合物半導体からなり、チャネル層を含む半導体層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層上において前記ゲート電極を挟むように配置されたソース電極およびドレイン電極と、を備え、前記チャネル層の表面の、少なくとも前記ゲート電極直下の領域が、窒素極性の表面を含む。

(もっと読む)

横型HEMTおよび横型HEMTの製造方法

【課題】高いアバランシュブレークダイン強度を有する横型HEMTと、その製造方法を提供する。

【解決手段】基板10と、基板上に配置された、第1導電型のチヤネルとなる第1層11、少なくとも部分的に上記第1層11の上に配置された電子供給層となる第2層12を有する。さらに、上記横型HEMTは、上記第1導電型に対して相補的な第2導電型の半導体物質を有し、少なくとも部分的に上記第1層11の中に配置された第3層13を有する。このためPNダイオードが上記第1層および第3層の間で形成され、PNダイオードは横型HEMTより低いブレークダウン電圧を有することにより、HEMTを高い電界から保護することができ、HEMTの劣化を防止できる。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

半導体デバイス、FETデバイスに非対称的なp/n接合を形成する方法及びFETデバイスを形成する方法(低電力消費のシリコン・オン・インシュレータ・デバイスのための非対称的なソース/ドレイン接合)

【課題】 非対称的なp/n接合を有する半導体デバイスを提供する。

【解決手段】 半導体デバイスは、バルク基板上に形成された埋め込み絶縁層と、埋め込み絶縁層上に形成され電界効果トランジスタ(FET)のボディ領域に対応する第1の型の半導体材料と、ボディ領域の互いに対向する側部に隣接するように埋め込み絶縁層の上方に設けられFETデバイスのソース領域及びドレイン領域に対応し且つ第1の型の半導体材料のバンドギャップと異なるバンドギャップを有する第2の型の半導体材料とを有し、FETのソース側のp/n接合の大部分は第1の型の半導体材料及び第2の型の半導体材料のうち狭いバンドギャップを有する半導体材料内に配置され、且つFETのドレイン側のp/n接合は、第1の型の半導体材料及び第2の型の半導体材料のうち広いバンドギャップを有する半導体材料内に配置される。

(もっと読む)

逆スタガ構造の薄膜トランジスタ及びその製造方法

【課題】生産性を向上させ、かつトランジスタ特性が良好な逆スタガ構造の薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】本発明にかかる逆スタガ構造の薄膜トランジスタは、ソース領域41、ドレイン領域42、及びチャネル領域43を有する結晶性半導体膜40を備える。また、薄膜トランジスタは、チャネル領域43上に形成された絶縁膜5と、ソース領域41及びドレイン領域42上に形成されたシリサイド層61とを備える。そして、チャネル領域43は、ソース領域41及びドレイン領域42における結晶粒よりも小さい結晶粒により構成される。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフリーク電流が低減した薄膜トランジスタを提供する。

【解決手段】本発明に係るシリコン薄膜トランジスタ10は、絶縁性基板7上に形成されたゲート電極1と、ゲート電極1を覆うように形成された絶縁膜2と、絶縁膜2上に形成された半導体層30であって、絶縁膜2を介してゲート電極1上にチャネル領域33を有する半導体層30と、チャネル領域33を挟むように、チャネル領域33の周囲に形成されたソース電極51、52およびドレイン電極61、62とを備えており、チャネル領域33は、微結晶シリコン領域32と、微結晶シリコン領域32よりも高抵抗であるアモルファスシリコン領域31とに分かれており、微結晶シリコン領域32とアモルファスシリコン領域31とがチャネル長方向に交互に並んでいる。

(もっと読む)

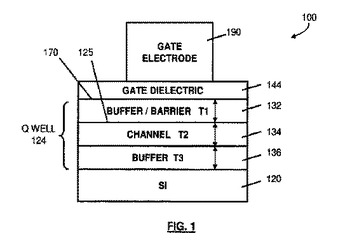

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスにおいてフォトレジスト構造等の追加工程を必要としない、非対称なDSS構造の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の側面に形成されたオフセットスペーサ13、23と、一方のオフセットスペーサ23の側面に形成されたゲート側壁27と、半導体基板2中のゲート絶縁膜21下に形成されたチャネル領域25と、半導体基板2内のチャネル領域25を挟む領域に形成され、チャネル領域25側に導電型不純物が偏析して形成されたエクステンション領域24aを有するソース・ドレイン領域24と、ソース・ドレイン領域24上にオフセットスペーサ13に接して形成されたシリサイド層16、及び、ゲート側壁27に接して形成されたシリサイド層26と、を有した半導体装置1とする。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細な活性層上にひずみ半導体素子を形成しても、活性層のひずみの緩和を抑制することを可能にする。

【解決手段】基板1と、基板上にメサ状に形成されひずみを有する第1半導体層であって、離間して設けられる第1導電型のソースおよびドレイン領域と、ソース領域とドレイン領域との間に設けられる第1導電型と異なる第2導電型のチャネル領域と、を有する第1半導体層3と、ソースおよびドレイン領域上に第1導電型の不純物を含むように形成され、第1半導体層のひずみを制御する第2および第3半導体層4aと、チャネル領域上に形成されたゲート絶縁膜10と、ゲート絶縁膜上に形成されたゲート電極12と、を備えている。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

バルク基板上に形成されたダブルゲート及びトライゲートトランジスタ及びそのトランジスタを形成するための方法

【解決手段】

FinFETS及びトライゲートトランジスタのような三次元トランジスタ構造が、強化されたマスキング形態によって形成することができ、それによりバルク半導体材質内での自己整合手法によるドレイン及びソース区域(211D,211S)、フィン(210)並びに分離構造(208A)の形成が可能になる。基本フィン構造(210)を画定した後、プレーナトランジスタ構造の高度に効率的な製造技術を用いることができ、それにより三次元トランジスタ構造の総合的な性能を更に高めることができる。

(もっと読む)

41 - 60 / 172

[ Back to top ]