Fターム[5F110HM15]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125) | オフセット (2,875) | LDD (2,472)

Fターム[5F110HM15]に分類される特許

41 - 60 / 2,472

半導体装置

【課題】液晶等の電気光学素子若しくは発光素子等を表示媒体として用いる表示装置及びその駆動方法を提供する。

【解決手段】劣化しやすいトランジスタのゲート電極に、オンしたトランジスタを介して信号を入力することで、劣化しやすいトランジスタのしきい値電圧のシフト及びオンしたトランジスタのしきい値電圧のシフトを抑制する。すなわち、高電位(VDD)がゲート電極に印加されているトランジスタを介して(若しくは抵抗成分を持つ素子を介して)、交流パルスを劣化しやすいトランジスタのゲート電極に加える構成を含んでいる。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

半導体装置

【課題】半導体チップが薄くなっても、応力による特性変化の少ない半導体装置を提供する。

【解決手段】SOI活性層のオリフラ方向の面方位を<100>、半導体支持基板の面方位を<110>とし、SOI活性層にはPチャネルMOSトランジスタ、半導体支持基板にはNチャネルMOSトランジスタを形成することで、NチャネルMOSトランジスタとPチャネルMOSトランジスタのどちらもピエゾ抵抗効果の角度度依存を持たないように配置することが可能となり、結果としてペアトランジスタ間のシフト量がそろい、半導体装置の特性が安定することとなる。

(もっと読む)

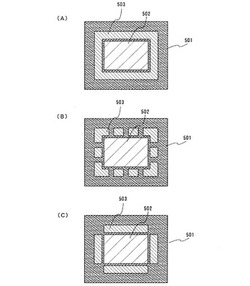

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する表示装置を作製する

ための技術を提供する。

【解決手段】固定基板上に、剥離層となる非晶質シリコン膜を介して樹脂基板を形成する

工程と、前記樹脂基板上に少なくともTFT素子を形成する工程と、前記非晶質シリコン

膜にレーザー光を照射することにより、前記非晶質シリコン膜において前記固定基板から

前記樹脂基板を剥離する工程とを行い、前記樹脂基板を用いた柔軟性を有する表示装置を

作製する。

(もっと読む)

半導体装置の製造方法及びプラズマドーピング装置

【課題】フィン型半導体領域の側面に不純物を導入して低抵抗の不純物領域を形成できるようにし、それによって、所望の特性を持つフィン型半導体装置を実現する。

【解決手段】基板11上にフィン型半導体領域13を形成した後、不純物含有ガスと酸素含有ガスとを用いて、フィン型半導体領域13に対してプラズマドーピングを行うことによって、フィン型半導体領域13の少なくとも側部に不純物導入領域27Bを形成する。

(もっと読む)

酸化物半導体膜の処理方法および半導体装置の作製方法

【課題】トランジスタに用いることが可能な、低抵抗領域を有する酸化物半導体膜を提供する。また、高速動作が可能な、酸化物半導体膜を用いたトランジスタを生産性高く提供する。また、高速動作が可能な、酸化物半導体膜を用いたトランジスタを有する高性能の半導体装置を生産性高く提供する。

【解決手段】酸化物半導体膜上に還元性を有する膜を成膜し、次に酸化物半導体膜から還元性を有する膜へ酸素の一部を移動させ、次に還元性を有する膜を介して酸化物半導体膜に不純物を注入した後、還元性を有する膜を除去することで、酸化物半導体膜に低抵抗領域を形成する。

(もっと読む)

液晶表示装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

誘電体分離基板および半導体装置

【課題】深い不純物拡散層の形成が容易な誘電体分離基板および半導体装置を提供する。

【解決手段】誘電体分離基板10では、半導体基板11に第1の厚さt1を有する絶縁膜12が設けられている。絶縁膜12上に第2の厚さt2を有する第1導電型の半導体層13が設けられている。半導体層13の下部に絶縁膜12に接して第2導電型の不純物拡散層14が部分的に設けられている。

(もっと読む)

発光装置

【課題】開口率の向上された発光装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線とを、プラスチック基板上に有する発光装置であって、配線は、容量の上に設けられ、容量は、配線の少なくとも一部と重なる領域を有する。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

EL表示装置

【課題】開口率を向上することができるEL表示装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線と有するEL表示装置である。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

41 - 60 / 2,472

[ Back to top ]