Fターム[5F110NN40]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 製法 (8,383) | 後処理 (815)

Fターム[5F110NN40]に分類される特許

161 - 180 / 815

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】化学量論的組成比を超える酸素を含む領域を有する非晶質酸化物半導体層と、該非晶質酸化物半導体層上に設けられた酸化アルミニウム膜とを含んで構成される半導体装置を提供する。該非晶質酸化物半導体層は、脱水又は脱水素化処理を行った結晶性又は非晶質酸化物半導体層に対して、酸素注入処理を行い、その後、酸化アルミニウム膜を設けた状態で450℃以下の熱処理を行うことで形成される。

(もっと読む)

表示装置の駆動方法

【課題】消費電力が少なく、表示品質の良い表示装置を提供することを課題の一とする。

【解決手段】第1の基板上に、端子部と、画素電極と、酸化物半導体を有するスイッチングトランジスタと、可視光に対して高い光感度を有する第1の光センサと、赤外光に光感度を有し、第1の光センサより可視光に対する光感度が低い第2の光センサを設ける。第1及び第2の光センサを用いて表示装置周囲の照度または色温度を検出して表示映像の輝度や色調を調整する。また、第1の基板に向かい合って第2の基板を設け、第2の基板上に対向電極を設ける。端子部からスイッチングトランジスタを介して対向電極へ電位を供給し、また、静止画を表示する期間において、スイッチングトランジスタを非導通状態として、対向電極を浮遊状態とする。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

表示装置及び液晶表示装置

【課題】酸化物半導体を用いたトランジスタを具備する画素において、開口率の向上を図る。

【解決手段】第1のトランジスタと、第1の画素電極とを有する第1の画素を有し、第2のトランジスタと、第2の画素電極とを有する第2の画素を有し、走査線として機能することができる配線を有し、第1のトランジスタは、酸化物半導体層を有し、酸化物半導体層はゲート絶縁膜を介して、配線と重なり、酸化物半導体層は、配線より幅の広い領域を有する表示装置又は液晶表示装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理を行った酸化物半導体膜を含み、且つ、作製工程において酸素ドープ処理されたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

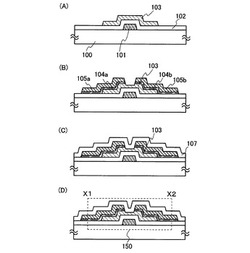

アクティブマトリクス基板及びそれを備えた表示パネル

【課題】フォトマスクの枚数を増やすことなく、酸化物半導体の半導体層を用いたTFTの特性の低下を抑制することにある。

【解決手段】マトリクス状の複数の画素電極Pと、各画素電極Pに接続されたTFT5と、互いに平行に延びる複数のソース線15aとを備え、TFT5が、絶縁基板10上のゲート電極11aと、ゲート電極11aを覆うゲート絶縁膜12aと、ゲート絶縁膜12a上でゲート電極11aに重なる酸化物半導体層13aと、酸化物半導体層13aに接続されたソース電極17a及びドレイン電極17bとを備え、ソース電極17a及びドレイン電極17bと酸化物半導体層13aとの間には、酸化物半導体層13aを覆う保護絶縁膜14aが設けられ、各ソース線15aは、金属材料により形成され、ソース電極17a及びドレイン電極17bは、各画素電極Pと同一材料により形成されている。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

アレイ基板及びその製造方法

【課題】アレイ基板及びその製造方法を提供する。

【解決手段】本発明による製造方法は、基板に無機材料の突起を形成するステップと;それぞれ第一透明導電層と第一金属層からなる反射領域パターン、ゲートライン及びゲートラインから分岐して出されるゲート電極と共通電極を形成するステップと;半導体層からなる活性化ランドパターンと第二金属層からなるデータラインパターンを形成し、活性化ランドパターン上でデータラインに接続されるソース電極とドレイン電極、及び半導体層からなるチャネルを形成するステップと;基板に無機材料を塗布し、無機材料に対して焼き戻し工程を行って一平坦層を形成し、ドレイン電極にビアホールを形成するステップと;反射領域に、ビアホールを介してドレイン電極に接続され且つ第二透明導電層からなる画素電極を形成するステップと、を有する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】ゲート絶縁層と、ゲート絶縁層の一方の面に接する第1のゲート電極と、ゲート絶縁層の他方の面に接し、第1のゲート電極と重畳する領域に設けられた酸化物半導体層と、酸化物半導体層と接するソース電極、ドレイン電極、及び酸化物絶縁層と、の積層構造を有し、酸化物半導体層の窒素濃度は2×1019atoms/cm3以下であり、ソース電極及びドレイン電極は、タングステン、白金及びモリブデンのいずれか一又は複数を含む半導体装置を提供する。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

表示装置の作製方法

【課題】表示装置の作製工程で紫外線の照射を行っても、酸化物半導体層を用いた薄膜ト

ランジスタのしきい値電圧のシフトを低減させることができる、表示装置の作製方法を提

供することを課題の一つとする。

【解決手段】少なくとも一回以上の紫外線の照射を行い、且つ酸化物半導体層を有する薄

膜トランジスタをスイッチング素子として用いる、表示装置の作製方法において、全ての

紫外線照射工程を終えた後で、紫外線照射による該酸化物半導体層のダメージを回復させ

る熱処理を行う表示装置の作製方法である。

(もっと読む)

半導体装置

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物

半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで

、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注

入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び

、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第1の結晶性酸化物半導体膜ともいう)を形成し、該酸化物半導体膜に酸素を導入して少なくとも一部を非晶質化し酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第2の結晶性酸化物半導体膜ともいう)を形成する。

(もっと読む)

薄膜トランジスタ

【課題】高移動度の薄膜トランジスタ、その製造方法及びその製造に用いるスパッタリングターゲットを提供する。

【解決手段】元素In,Ga及びZnを下記領域1、2又は3の原子比の範囲で含む酸化物を活性層とし、電界効果移動度が25cm2/Vs以上である薄膜トランジスタ。

領域1

0.58≦In/(In+Ga+Zn)≦0.68

0.15<Ga/(In+Ga+Zn)≦0.29

領域2

0.45≦In/(In+Ga+Zn)<0.58

0.09≦Ga/(In+Ga+Zn)<0.20

領域3

0.45≦In/(In+Ga+Zn)<0.58

0.20≦Ga/(In+Ga+Zn)≦0.27

(もっと読む)

161 - 180 / 815

[ Back to top ]