Fターム[5F110NN40]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 製法 (8,383) | 後処理 (815)

Fターム[5F110NN40]に分類される特許

141 - 160 / 815

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

る。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて

、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及

び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層

する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガス

を用いた酸化シリコン膜で形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置

【課題】連想メモリは一つのメモリセル内の素子数が多く、一つのメモリセルの面積が大きくなりやすい。そこで、一つのメモリセルの面積を小さくする。

【解決手段】読み出し用のトランジスタのチャネル容量(ゲート電極とチャネル形成領域との間の容量)を用いて電荷の保持を行う。つまり、読み出し用のトランジスタを電荷保持用のトランジスタとして兼用する。また、読み出し用且つ電荷保持用のトランジスタのゲートに電荷供給用のトランジスタのソース又はドレインの一方を電気的に接続する。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

【課題】特定のトランジスタのゲートの電位に応じて記憶情報の判別が行われる半導体装置において、当該トランジスタのしきい値電圧のばらつきの低減と、長期間に渡る情報の保持とを両立することで情報の保持特性に優れる半導体装置を提供すること。

【解決手段】チャネル領域が酸化物半導体によって形成されるトランジスタのソース又はドレインのみに電気的に接続されるノードにおいて電荷の保持(情報の記憶)を行う。なお、当該ノードにソース又はドレインが電気的に接続されるトランジスタは、複数であってもよい。また、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

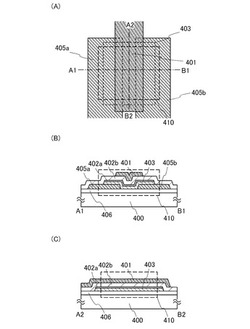

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置およびその作製方法

【課題】In−Sn−Zn−O系半導体を用いた半導体装置を作製する際の加工技術を確立する。

【解決手段】Cl2または、BCl3または、SiCl4などの塩素を含むガスを用いたドライエッチングによりIn−Sn−Zn−O系半導体層を選択的にエッチングする。In−Sn−Zn−O系半導体層上に接して形成する導電層を選択的に除去してソース電極層及びドレイン電極層を形成する場合、塩素を含むガスに加えて酸素を含むガス、またはフッ素を含むガスを用い、In−Sn−Zn−O系半導体層がほとんど除去されないように導電層を選択的にエッチングすることができる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】非接触にて、被写体の位置情報の取得を容易に行うことができる固体撮像装置、または半導体表示装置の提供。

【解決手段】第1入射方向から第1入射角を有する光が入射する複数の第1フォトセンサと、第1入射方向とは異なる第2入射方向から第2入射角を有する光が入射する複数の第2フォトセンサとを有し、複数の第1フォトセンサのうち、第1入射方向の上流側の一つの第1フォトセンサの方が、第1入射方向の下流側の他の一つの第1フォトセンサよりも、第1入射角が大きく、複数の第2フォトセンサのうち、第2入射方向の上流側の一つの第2フォトセンサの方が、第2入射方向の下流側の他の一つの第2フォトセンサよりも、第2入射角が大きい。

(もっと読む)

表示装置及び電子機器

【課題】信号線駆動回路が有するスイッチ回路を画素部と同じ基板上に配置する構成において、スイッチ回路を構成するトランジスタサイズを縮小し、データを供給することによる信号線の充放電を行う際の回路内の負荷を削減する

【解決手段】映像信号が入力される画素部と、映像信号の画素部への出力を制御するためのスイッチ回路部を有する信号線駆動回路を有し、スイッチ回路部は、絶縁基板上において、電界効果移動度が少なくとも80cm2/Vs以上であるトランジスタを有し、トランジスタは、酸化物半導体層を有する。

(もっと読む)

半導体装置

【課題】大電力の制御を行う、高耐圧の半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の、ゲート電極と重畳する酸化物半導体層と、酸化物半導体層と接し、端部をゲート電極と重畳するソース電極及びドレイン電極と、を有し、ゲート電極と酸化物半導体層が重畳する領域において、ゲート絶縁層は、ドレイン電極と端部を重畳する第1の領域と、前記第1の領域と隣接する第2の領域と、を有し、第1の領域の静電容量は第2の領域の静電容量より小さいトランジスタを提供すること。

(もっと読む)

表示装置及び液晶表示装置

【課題】酸化物半導体を用いたトランジスタを具備する画素において、開口率の向上を図る。

【解決手段】第1のトランジスタと、第1の画素電極とを有する第1の画素を有し、第2のトランジスタと、第2の画素電極とを有する第2の画素を有し、走査線として機能することができる配線を有し、第1のトランジスタは、酸化物半導体層を有し、酸化物半導体層はゲート絶縁膜を介して、配線と重なり、酸化物半導体層は、配線より幅の広い領域を有する表示装置又は液晶表示装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程におい

て、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。酸素ドープ処

理されたゲート絶縁膜、熱処理による脱水化または脱水素化処理された酸化物半導体膜を

有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジ

スタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることが

できる。

(もっと読む)

141 - 160 / 815

[ Back to top ]