Fターム[5F110NN74]の内容

Fターム[5F110NN74]の下位に属するFターム

ゲート電極を共有しているもの (6)

Fターム[5F110NN74]に分類される特許

21 - 40 / 349

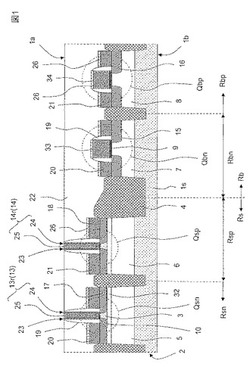

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

光検出装置及び光検出装置の駆動方法

【課題】ノイズによる影響を抑制する。

【解決手段】光検出回路と、差分データ生成回路と、データ入力選択回路と、を具備する。光検出回路は、光データ信号を生成する機能を有する。また、差分データ生成回路は、第1のデータ信号及び第2のデータ信号が入力され、第1のデータ信号のデータと第2の信号のデータとの差分データを生成する機能を有する。また、データ入力選択回路は、光データ信号のデータを、第1のデータ信号のデータみなすか第2のデータ信号のデータとみなすかを決定する機能を有する。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置

【課題】新規な構成を有する半導体装置である。

【解決手段】第1の素子を有し、第2の素子を有し、トランジスタを有し、容量を有し、第1の素子の出力は、第2の素子の入力と電気的に接続され、第2の素子の出力は、第1の素子の入力と電気的に接続され、第1の素子の入力は、入力端子と電気的に接続され、第1の素子の出力は、出力端子と電気的に接続され、トランジスタのソース及びドレインの一方は、容量の一方の電極と電気的に接続され、トランジスタのソース及びドレインの他方は、入力端子と電気的に接続され、トランジスタのチャネル形成領域は、結晶を有する酸化物半導体を有する。結晶を有する酸化物半導体を有するトランジスタはリーク電流が非常に小さいため、データを保持することができる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

半導体装置

【課題】半導体チップが薄くなっても、応力による特性変化の少ない半導体装置を提供する。

【解決手段】SOI活性層のオリフラ方向の面方位を<100>、半導体支持基板の面方位を<110>とし、SOI活性層にはPチャネルMOSトランジスタ、半導体支持基板にはNチャネルMOSトランジスタを形成することで、NチャネルMOSトランジスタとPチャネルMOSトランジスタのどちらもピエゾ抵抗効果の角度度依存を持たないように配置することが可能となり、結果としてペアトランジスタ間のシフト量がそろい、半導体装置の特性が安定することとなる。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

21 - 40 / 349

[ Back to top ]