Fターム[5F140AA26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | エッチングダメージの防止 (163)

Fターム[5F140AA26]に分類される特許

1 - 20 / 163

半導体装置及び半導体装置の製造方法

半導体装置の製造方法

半導体装置の製造方法

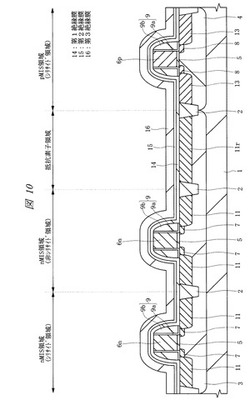

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタのソース又はドレイン用の拡散層を形成するにあたって形成されるシリコン膜に表面凹凸を発生させない半導体装置の製造方法を提供する。

【解決手段】複数の半導体ピラーを形成する工程と、隣り合う前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程と、前記絶縁膜の前記溝の底部に近い領域に側面開口を形成する工程と、前記溝の内部を覆うようにシリコン膜からなる被覆膜を形成する工程と、前記被覆膜上に前記半導体ピラー内へ拡散させる不純物で構成された不純物層を形成する工程と、前記不純物を、前記側面開口を塞ぐように形成されている前記被覆膜を通して前記半導体ピラー内に熱拡散させてソース又はドレイン用の拡散層を形成する工程と、を含む。前記被覆膜の成膜温度を510℃より高く度550℃未満の範囲とすることにより、非晶質状態のシリコン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの特性のばらつきを低減するために有利な技術を提供する。

【解決手段】MOSトランジスタを含む半導体装置の製造方法は、半導体基板の上に形成された第1絶縁膜の上にゲート電極材料層を形成する工程と、前記ゲート電極材料層の上にエッチングマスクを形成する工程と、前記ゲート電極材料層をパターニングすることによりゲート電極を形成する工程と、前記ゲート電極が形成された前記半導体基板の上に第2絶縁膜を形成する工程とを含み、前記ゲート電極を形成する工程では、前記ゲート電極材料層がパターニングされるとともに、少なくとも、前記ゲート電極の側面の下部と、前記第1絶縁膜のうち前記側面に隣接する部分とを保護する保護膜が形成され、前記第2絶縁膜を形成する工程では、前記保護膜を覆うように前記第2絶縁膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】ノーマリオフ型のHEMT構造を有し、かつ優れたデバイス特性を有する窒化物半導体装置およびその製造方法を提供する。

【解決手段】窒化物半導体装置は、窒化物半導体からなる電子走行層3と、電子走行層3に積層され、電子走行層3とはAl組成が異なり、Alを含む窒化物半導体からなる電子供給層4と、電子供給層4と電子走行層3との界面に連続する界面を有し、電子走行層3上に形成された酸化膜11と、酸化膜11を挟んで電子走行層3に対向するゲート電極8とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造する。

【解決手段】半導体装置の製造方法は、半導体基板50上に絶縁膜を形成する工程と、絶縁膜上に、ゲート電極20およびハードマスク34を順に積層してなる積層体10を形成する工程と、積層体10をマスクとして、半導体基板50にイオン注入を行う工程と、積層体10の側面上に保護膜44を形成する工程と、エッチングによりハードマスク34を除去する工程と、エッチングにより保護膜44を除去する工程と、を備える。

(もっと読む)

シリコンに対する誘電材料の選択エッチング方法及びシステム

【課題】 本発明はドライプラズマエッチングを用いた基板のエッチング方法に関する。

【解決手段】 ドライプラズマエッチングシステム内で誘電体層をシリコン及びポリシリコンに対して選択的な均一エッチングを行う方法及びシステムが記載されている。エッチング用化学は、たとえばCH2F2やCHF3のようなフルオロハイドロカーボンを有する。高いエッチング選択性及び受容可能な均一性は、CH2F2の流速やドライプラズマエッチングシステムと結合する出力を含むプロセス条件を選択することによって実現されて良い。それにより、エッチングプラズマ中での活性エッチングラジカルとポリマー生成ラジカルとの適切なバランスがとられる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】イオン注入により半導体基板1にエクステンション領域EXを形成してから、ゲート電極GEの側壁上にサイドウォールスペーサSWを形成し、その後、イオン注入により半導体基板1にソース・ドレイン領域SDを形成する。サイドウォールスペーサSWを形成するには、半導体基板1上にゲート電極GEを覆うように絶縁膜6を形成してから、この絶縁膜6を異方性エッチングし、その後、半導体基板1上にゲート電極GEを覆うように絶縁膜7を形成してから、この絶縁膜7を異方性エッチングすることで、ゲート電極GEの側壁上に残存する絶縁膜6,7からなるサイドウォールスペーサSWを形成する。絶縁膜6のエッチング工程では、絶縁膜6をアンダーエッチングまたはジャストエッチングし、絶縁膜7のエッチング工程では、絶縁膜7をオーバーエッチングする。

(もっと読む)

エッチング方法及び装置

【課題】基板に形成された絶縁膜をエッチングするとき、絶縁膜の下地に酸素プラズマの悪影響が生ずるのを防止できるエッチング方法を提供する

【解決手段】本発明のエッチング方法は、絶縁膜222をプラズマ化させた処理ガスに晒し、絶縁膜222を厚さ方向に途中までエッチングする第一のエッチング工程と、第一のエッチング工程の終了後に残存する絶縁膜222を酸素プラズマに晒し、残存する絶縁膜222の表面に堆積した堆積物を除去する堆積物除去工程と、残存する絶縁膜222をプラズマ化させた処理ガスに晒し、残存する絶縁膜222をエッチングする第二のエッチング工程と、を備える。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】電界効果トランジスタにおけるゲート電極の汚染を防止し、かつゲート電極上に形成されるマスク膜の膜厚を薄くする。

【解決手段】基板10上にゲート絶縁膜100を形成する。次いでゲート絶縁膜100上にゲート電極膜120を形成する。ゲート電極膜120の一部上にマスク膜230を形成する。マスク膜230をマスクとしたエッチングによりゲート電極膜120を選択的に除去する。そして、マスク膜230とゲート電極膜120の側面に接するようゲート側壁膜130を形成する。マスク膜230は少なくとも第1膜200、第2膜210、及び第3膜220をこの順に積層した積層膜により構成される。第2膜210は、ゲート側壁膜130に対して第3膜220よりも高いエッチング選択比を有する。第3膜220は、ゲート電極膜120に対して第2膜210よりも高いエッチング選択比を有する。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

半導体デバイス、半導体デバイスの製造方法および半導体デバイスの製造装置

【課題】RLSAにおける高密度プラズマを実現し、処理速度の上昇を可能とする。

【解決手段】ゲート電極を基板表面にゲート絶縁膜を介して形成し、絶縁膜をゲート絶縁膜の側面に形成し、基板表面を酸素プラズマで曝す工程を含む半導体デバイスの製造方法である。酸素プラズマの基板表面近傍の電子温度が約1.5eV以下となることを特徴とする。

(もっと読む)

1 - 20 / 163

[ Back to top ]