Fターム[5F140AA37]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 試験、測定、検査(モニタ素子) (119)

Fターム[5F140AA37]に分類される特許

1 - 20 / 119

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

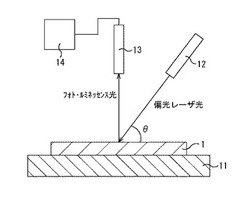

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体ガスセンサ

【課題】従来技術を発展させた半導体ガスセンサを提供すること。

【解決手段】第1の端子部分が、半導体本体(20)の表面に設けられたパッシベーション層(30)を貫通する第1の成形部分(112)を有し、該第1の成形部分(112)は、参照電位に接続された導電性層(115)を備えた底面を有し、該第1の端子部分と制御電極(100)とは第1の接合材(130)を用いて電気的接続かつ摩擦接続的に結合されている。第2の端子部分と前記制御電極(100)とは第2の接合材(140)を用いて少なくとも摩擦接続的に結合されており、前記第1の接合材(130)は前記成形部分を少なくとも部分的に充填し、前記制御電極(100)と前記導電性層(115)とを接続する。

(もっと読む)

半導体装置及び半導体装置の検査方法

【課題】狭いゲート電極間にコンタクトを配置することなく、オーバーラップ容量を測定する。

【解決手段】この半導体装置は、下記のような第1TEGパターン(不図示)を備えている。第1TEGパターンは、素子分離領域500と、素子分離領域500に形成された開口部(不図示)と、開口部上に設けられ、互いに平行に延伸した複数のゲート電極300と、開口部のゲート電極300で覆われていない部分に形成された拡散領域200と、を備えている。ここで、ゲート電極300の一方の端部は、開口部の外縁よりも内側に配置されている。また、第1コンタクト240は、ゲート電極300の一方の端部と、開口部の外縁の間に位置して、拡散領域200に接続している。一方、第2コンタクト340は、ゲート電極300に接続している。

(もっと読む)

絶縁物/半導体界面の評価方法及び評価装置

【課題】MISあるいはMOS界面の欠陥密度(界面準位密度)を簡便かつ高い精度で求める。

【解決手段】絶縁物/半導体界面における界面欠陥に起因する容量CITが無視できる程度の高周波におけるC−V特性を元に、酸化膜容量の影響を排除した半導体容量(CD+CIT)を計算するステップと、1/(CD+CIT)2を低周波(準静電的)C−V特性から計算される表面ポテンシャルψsに対してプロットするステップと、ψs−1/(CD+CIT)2プロットの外挿値が原点を通るように定数項を定めることにより、表面ポテンシャルψsの絶対値を確定するステップと、を有することを特徴とする絶縁物/半導体界面の評価方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを向上可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、半導体基板上に形成される検査用トランジスタおよび製品用トランジスタのソースおよびドレインを活性化させるアニール処理を行うアニール工程と、アニール工程後における検査用トランジスタのゲート、ソースおよびドレインをシリサイド化させる検査用サリサイド工程と、検査用サリサイド工程後における検査用トランジスタの特性を測定する測定工程と、測定工程によって測定された特性と所望の特性との差分とに基づいて製品用トランジスタの特性を所望の特性へ近付ける特性調整アニール処理を行う特性調整アニール工程と、特性調整アニール工程後における製品用トランジスタのゲート、ソースおよびドレインをシリサイド化させる本サリサイド工程とを含む。

(もっと読む)

シリコン単結晶ウェーハの評価方法

【課題】 本発明は、デバイス製造工程終了後(デバイス製品)のGOI特性の評価結果と近いGOI特性の評価結果を、ウェーハ段階で事前に得ることができ、デバイス製造工程終了後のウェーハ品質に起因する耐圧不良を予測することが可能となるシリコン単結晶ウェーハの評価方法を提供する。

【解決手段】デバイス製造に用いるシリコン単結晶ウェーハの評価方法であって、少なくとも、シリコン単結晶ウェーハの表面にゲート酸化膜を形成した後、デバイス製造シミュレーション熱処理を行ない、その後、前記ゲート酸化膜のGOI特性を評価することを特徴とするシリコン単結晶ウェーハの評価方法。

(もっと読む)

半導体装置の評価方法

【課題】pチャネル型電界効果トランジスタのNBTIをウエハ面内において漏れなく評価することにより、信頼性評価の充実を図り、信頼性の高いpチャネル型電界効果トランジスタを提供する。

【解決手段】劣化過程、回復過程、および再劣化過程をストレス試験の1サイクルとし、1つのpチャネル型電界効果トランジスタに対して上記1サイクルを複数回繰り返し行い、複数の劣化過程におけるしきい値電圧の劣化量または動作電流の劣化量を抽出して回復レス劣化評価を行い、複数の回復過程におけるしきい値電圧の劣化量および動作電流の劣化量を抽出して回復レス劣化評価を行う。

(もっと読む)

化学的感受性電界効果トランジスタのための製造方法

【課題】使用可能な処理技術と材料の数、ならびに処理技術の順序における変更可能性を高めることである。

【解決手段】本発明は、とりわけガスセンサ用の化学的感受性電界効果トランジスタである電界効果トランジスタの製造方法に関する。使用可能な処理技術と材料の数、ならびに処理技術の順序における変更可能性を高めるために、本方法の枠内で、ゲート絶縁保護層(3)が形成され、このゲート絶縁保護層は、ゲート絶縁層(2)をさらなるプロセス化の際に環境の影響から保護し、ゲート電極層形成前に部分的にまたは完全に除去される。さらに本発明は、この種の電界効果トランジスタおよびその使用法に関する。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法

【課題】MOSトランジスタの電気的特性を高精度に再現する。

【解決手段】図形情報生成手段と、パラメータ補正量計算手段と、回路シミュレーション手段とを備える回路シミュレーション装置によって以下の方法で、回路シミュレーションを行う。その方法は、チャネル領域とSTI領域との境界における、チャネル長方向の中点を特定する。そして、ゲート幅方向を縦方向とし、その中点を原点としてそのMOSトランジスタとそのMOSトランジスタの隣の拡散層との距離を縦方向隣接拡散層距離とするとき、その縦方向隣接拡散層距離を、そのチャネル長方向の位置Xに応じて変化する縦方向の距離の関数として特定する。その縦方向隣接拡散層距離の関数と重み付け関数とを掛け合わせた乗算式を生成し、その乗算式に基づいて、パラメータ補正量を算出する。

(もっと読む)

設計支援装置、設計支援方法及び設計支援プログラム

【課題】複数のゲートが同一の拡散領域内に並列に配置されている場合において、トランジスタにおける、機械的応力による移動度の変動を見積もることを目的とする。

【解決手段】開示の装置は、回路データ生成手段と、パラメータ決定手段と、を備える。回路データ生成手段は、半導体集積回路における回路素子のレイアウト情報を基に、当該回路素子の物理特性を反映した回路データを生成する。パラメータ決定手段は、同一の拡散領域内に複数のゲートが設けられている場合において、ゲート電極として機能するゲートを有するトランジスタにかかる機械的応力に関するパラメータを、複数のゲートのレイアウト形状に応じて一意に決定する。ここで、回路データ生成手段は、当該パラメータを用いて、トランジスタにおける、機械的応力の影響を反映した移動度を求め、求められた移動度を回路データに反映する。

(もっと読む)

MOSトランジスタのシミュレーションパラメータの抽出方法

【課題】ゲートとドレインとの重なり部分の容量であるゲートオーバーラップ容量を精度よく抽出する。

【解決手段】本発明の一態様に係るシミュレーションパラメータの抽出方法は、コンタクトプラグ数のみが異なる複数のレイアウトパターンのそれぞれについて、所定のバイアス電圧下におけるゲート−ドレイン間の容量を測定して真のゲートオーバーラップ容量を含む測定値を求め、コンタクトプラグとゲートとの間の寄生容量を求めるためのモデルパラメータを変化させてシミュレーションを行って得られるコンタクトプラグとゲートとの間のコンタクト寄生容量を測定値から減算することによりゲートオーバーラップ容量演算値を求め、当該ゲートオーバーラップ容量演算値がコンタクトプラグの数によらず略一定となるモデルパラメータにおける当該ゲートオーバーラップ容量演算値を真のゲートオーバーラップ容量として抽出する。

(もっと読む)

ゲート絶縁膜の絶縁破壊寿命の評価方法、ゲート絶縁膜の絶縁破壊寿命の評価装置、ゲート絶縁膜の絶縁破壊寿命の評価用のプログラム

【課題】ソフトブレークダウンの判定条件を一意に決定することを可能にする、ゲート絶縁膜の絶縁破壊寿命の評価方法を提供する。

【解決手段】MOS型素子のゲート絶縁膜の絶縁破壊寿命を評価する際に、MOS型素子のゲート絶縁膜のソフトブレークダウンに至る寿命分布のワイブル傾きを決定する工程S1と、その後、決定したワイブル傾きから、ソフトブレークダウンの検知条件を決定する工程S2と、決定した検知条件を使用して、絶縁破壊試験を行う工程S3とを行う。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

モデルパラメータ決定装置、モデルパラメータ決定方法及びプログラム

【課題】半導体集積回路を製造するプロセスを変更した場合において、デバイスモデルによって変更後のプロセスにより製造された半導体素子を表すためにデバイスモデルに含まれるモデルパラメータを容易に決定できるようにする。

【解決手段】モデルパラメータ決定装置は、第1の製法により製造された半導体素子を特徴付ける第1の物理パラメータ群と、半導体素子の特性を表すためのデバイスモデルに含まれるモデルパラメータ群であって第1の製法により製造された半導体素子を表すための第1のモデルパラメータ群と、第2の製法により製造された半導体素子を特徴付ける第2の物理パラメータ群とを入力し、第2の製法により製造された半導体素子の特性を当該デバイスモデルによって表すためのモデルパラメータ群を、第1の物理パラメータ群及び第1のモデルパラメータ群並びに第2の物理パラメータ群に基づいて決定する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と半導体基板間のリーク位置を、TEG素子を用いて非接触で迅速に測定することができる半導体装置の製造方法を提供する。

【解決手段】

TEG素子101は、絶縁分離溝2により画定さるTEG素子形成領域8上にゲート絶縁膜3を介して形成された一端が半導体基板1に接続されたゲート電極4と、少なくともゲート電極の両側に形成された不純物領域5aと、不純物領域より深い位置に素子形成領域の底全面を塞ぐように設けられ、不純物領域を半導体基板から電気的に絶縁する絶縁分離層7とを有する。荷電粒子ビームを不純物領域5aの一端及び他端に照射したときの内部抵抗R1、R2の差、及び不純物領域5aの両端間の抵抗Robを用いて、リーク位置を決定する。

(もっと読む)

半導体装置設計用シミュレーション装置、半導体装置設計用シミュレーション方法、ならびに半導体装置およびその製造方法

【課題】半導体装置の動作を実用上許容できる時間内で、かつ、高い精度で予測または再現し得る半導体装置設計用シミュレーション方法を提供する。

【解決手段】ソース・ドレイン間において、第1の時刻において準静的な定常状態で記述されるキャリアの密度と、第1の時刻よりも前の第2の時刻において過渡状態で記述されるキャリアの密度との差の少なくとも一部を、第1の時刻と第2の時刻との間におけるキャリアの遅延に応じて第2の時刻において過渡状態で記述されるキャリアの密度に加え、第1の時刻におけるキャリアの密度を過渡状態で記述する。ソース・ドレイン間の定常電流と準静的なキャリアの密度の時間変化の割合としての変位電流との和として、ソース・ドレイン間の過渡電流を記述する。準静的なキャリアの密度が過渡電流を満たすとして、準静的な前記キャリアの密度を非準静的なモデルとして記述する。

(もっと読む)

直列電界効果型トランジスタのパラメータフィッティング方法

【課題】 直列接続電界効果型トランジスタの回路モデルパラメータのフィッティング方法に関し、多段直列接続電界効果型トランジスタの回路モデルパラメータの効率的な抽出手順を提供し、モデル化を実施可能にする。

【解決手段】 多段直列接続電界効果型トランジスタの評価テスト用デバイスを用意し、複数のゲート電極に印加する電圧を制御して電気特性を評価し、パラメータ変数の基準値を孤立電界効果型トランジスタのモデル変数で設定し、さらに、パラメータ変数の微小変動分を加える形で回路モデルを作成し、次いで、評価した電気特性の多数のバイアス点とパラメータ変数の微小変動分の関係を、評価関数で評価し、評価関数を最小化することで微小変動分の変数の最適解を求め、最適解を多数の多段直列接続電界効果型トランジスタの評価テスト用デバイスについて求めてレイアウト変数の関数としてモデル化する。

(もっと読む)

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

1 - 20 / 119

[ Back to top ]