Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

161 - 180 / 555

半導体装置及びその製造方法

【課題】微細化し、サーマルバジェットの小さなアニールプロセスを用いてトランジスタを作製しても、リーク電流の増大を抑制できる半導体装置を提供すること。

【解決手段】第1導電型の半導体基板上に絶縁膜を介してゲート電極を有し、前記ゲート電極とは絶縁された形で、前記ゲート電極の直下の前記半導体基板のチャネル領域の両側に、第2導電型の不純物がドーピングされたソース・ドレイン領域を有し、前記ソース・ドレイン領域と前記チャネル領域の間に、前記ソース・ドレイン領域と同じ第2導電型であり、前記ソース・ドレイン領域よりも浅く、前記ソース・ドレイン領域と繋がったエクステンション領域を有し、前記エクステンション領域の近傍の第1導電型の領域に、周囲の領域よりも格子欠陥密度の高い高密度欠陥領域が局所的に形成され、前記高密度欠陥領域には、点欠陥が集合した点欠陥集合体が含まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】NMOSFETの高誘電率膜に第1金属を拡散させ、かつPMOSFETの高誘電率膜に第2金属を拡散させるときに、高誘電率膜上に異物が生じることを抑制する。

【解決手段】NMOSFET形成領域80とPMOSFET形成領域82に第1金属を含む膜16を形成し、PチャネルMOSFET形成領域82から膜16を除去する。次いで、NチャネルMOSFET形成領域80とPチャネルMOSFET形成領域82に高誘電率膜20を形成する。次いで、NチャネルMOSFET形成領域80とPチャネルMOSFET形成領域82に第2金属を含む膜22を形成し、NチャネルMOSFET形成領域80から膜22を除去する。次いで半導体基板10を熱処理することにより、第1金属および第2金属を高誘電率膜20の中に拡散させて第1高誘電率膜58及び第2高誘電率膜60を形成する。

(もっと読む)

半導体装置の評価方法、評価装置、および、評価プログラム

【課題】従来よりも正確な信頼性寿命を簡単に予測することのできる半導体装置の評価方法、評価装置、および、評価プログラムを提供する。

【解決手段】PMOSトランジスタのゲート電極にストレス電圧を一定時間印加するストレス電圧印加ステップS42と、一定時間の経過後、ドレイン電流Idを測定する測定ステップS43と、ゲート電極にストレス電圧より絶対値の小さい回復電圧を一定時間印加する回復電圧印加ステップS45と、一定時間の経過後、ドレイン電流Idを測定する測定ステップS46と、測定ステップS43で測定したドレイン電流Idと、測定ステップS46で測定したドレイン電流Idとから、ドレイン電流劣化率ΔIdと作動時間の関係を近似した近似式を求める近似ステップと、近似式のドレイン電流劣化率ΔIdに、信頼性寿命の判断基準となる数値を代入することにより、信頼性寿命を算出する算出ステップと、を含む。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

コンタクト形成方法、半導体装置の製造方法、および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】半導体と接した第1の金属層を酸化防止用の第2の金属層で覆った状態で、第1の金属層のみをシリサイド化し、酸素混入のないシリサイド層を形成する。第1の金属層の材料として、半導体との仕事関数の差が所定の値となるような金属が用いられ、第2の金属層の材料として、アニール温度で第1の金属層と反応しない金属が用いられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体層に形成したリセスにモフォロジの良好な別の半導体層をエピタキシャル成長させる。

【解決手段】Si基板上にゲート絶縁膜、ゲート電極及びサイドウォールスペーサを形成した後(ステップS1,S2)、そのSi基板のソース・ドレイン領域を形成する部分に、ドライエッチングで第1リセスを形成する(ステップS3)。そして、ドライエッチングによってエッチングダメージが生じた第1リセスの表層部をウェットエッチングで除去することによって第2リセスを形成した後(ステップS4)、第2リセスにSiGe層をエピタキシャル成長させる(ステップS5,S6)。これにより、Si基板に形成したリセスに、モフォロジの良好なSiGe層を形成することが可能になる。

(もっと読む)

ファセットされたシリサイドコンタクトを有する半導体デバイス及び関連する製造方法

【解決手段】

開示される主題は、半導体トランジスタデバイス及び、従来のシリサイドコンタクトと比較して増大された実効サイズを有するシリサイドコンタクトを形成するために利用することができる関連する製造技術に関する。ここに開示されるプロセスに従って製造される半導体デバイス(200)は、半導体材質(102)の層と、半導体材質(102)の層を覆うゲート構造(112,128)とを含む。チャネル領域(218)が半導体材質(102)の層内に形成され、チャネル領域(218)はゲート構造(112,128)の下層となる。半導体デバイス(200)はまた、半導体材質(102)の層内のソース及びドレイン領域(216)を含み、チャネル領域(218)はソース及びドレイン領域(216)の間に配置される。また、半導体デバイス(200)はソース及びドレイン領域(216)を覆うファセット形状シリサイドコンタクト区域(210,308,406)を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

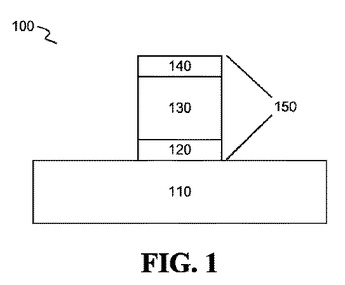

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程においてストレッサー膜などから発生する水素によるp型MOSトランジスタの駆動力低下を防止する。

【解決手段】半導体装置は、n型活性領域13B上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16Bと、ゲート絶縁膜15及びゲート電極16Bの側面に形成された内側サイドウォール17及び外側サイドウォール20Bと、p型ソースドレイン領域21Bと、内側サイドウォール17の側面及び外側サイドウォール20Bの側面における少なくとも底部に形成され、水素に対してバリア性を有する絶縁性の水素バリア膜23とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性が高く良好な特性を有する半導体装置を提供する。

【解決手段】半導体基板101上に形成され、チャネル領域とチャネル領域を挟むソース/ドレイン・エクステンション領域108の少なくとも一部とを含むSiGe膜104aと、半導体基板の表面領域に形成され、ソース/ドレイン・エクステンション領域に接するソース/ドレイン・コンタクト領域110と、SiGe膜上に形成されたゲート絶縁膜105およびゲート電極106を有するゲート構造と、SiGe膜上に形成され、且つゲート構造の側面に形成された第1の側壁膜107と、SiGe膜上に形成され、且つ第1の側壁膜上に形成された第2の側壁膜109と、ソース/ドレイン・コンタクト領域上に形成され、且つSiGe膜の側面および第2の側壁膜上に形成された第3の側壁膜111と、ソース/ドレイン・コンタクト領域上に形成されたシリサイド膜112と、を備える。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ゲート絶縁膜上のゲート電極の仕事関数を増大させることができ、低い閾値電圧の半導体装置を提供する。

【解決手段】半導体装置1は、基板(シリコン基板2)と、シリコン基板2上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極(Pt含有Ni3Si電極19)を備え、Pt含有Ni3Si電極19が、ゲート絶縁膜4とPt含有Ni3Si電極19との接する部分に、第一金属を含む第一金属シリサイド、および第二金属を含む第二金属シリサイドまたは第二金属を含み、第二金属を含む第二金属シリサイドが、第二金属を含む第二金属シリサイド中のシリコンに対する第二金属の組成比が1より大きい金属リッチシリサイドであることを特徴とする。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体領域2と、半導体領域に離間して形成されたソースおよびドレイン領域12a、12bと、ソース領域とドレイン領域との間の半導体領域上に形成され、シリコンと酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、第1絶縁膜と第2絶縁膜との界面を含む界面領域7に、Be、Bから選ばれた少なくとも1つの第1添加物質が導入されており、第1添加物質の面密度が、界面領域内の第1絶縁膜側においてピークを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高誘電率膜と金属ゲート電極を用いたMOS型の半導体装置のフラットバンド電圧のロールオフ効果を抑制することができ、しきい値電圧を適正な範囲に制御することのできる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に形成されたゲート絶縁膜2と、このゲート絶縁膜2の上に形成された金属ゲート電極3とを有する半導体装置であって、ゲート絶縁膜2が、第1の絶縁膜2aと、第1の絶縁膜2aの上に形成され、第1の絶縁膜2aより高い誘電率を有する第2の絶縁膜2bと、第2の絶縁膜2bの上に形成された第3の絶縁膜2cとを具備している。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、良好な移動度を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

(もっと読む)

半導体装置

【課題】ESD保護素子としてMISトランジスタを備えた半導体装置において、MISトランジスタの面積の増大を招くことなく、MISトランジスタ内の動作均一性を高める。

【解決手段】半導体基板10に形成されたMISトランジスタを備えた半導体装置であって、MISトランジスタは、半導体基板10に形成されたドレイン拡散層15と、半導体基板10上にチャネル幅方向に沿って互いに間隔を空けて配置され、ドレイン拡散層15をチャネル幅方向に沿って互いに分割する複数の分割体14と、半導体基板10上に分割体14を覆うように形成され、ドレイン拡散層15のチャネル幅方向に応力を生じさせる応力膜17とを備えている。

(もっと読む)

161 - 180 / 555

[ Back to top ]