Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

141 - 160 / 555

半導体装置

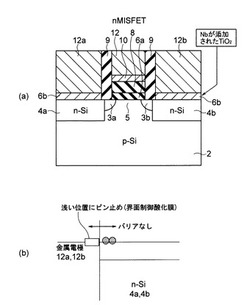

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置の製造方法

【課題】 閾値電圧の低い金属ゲート電極においてPMISFETの製造方法を提供する。

【解決手段】 半導体基板10上にPMISFETを作製する方法であって、半導体基板10上に絶縁膜20を形成する工程と、半導体基板10及び絶縁膜20をハロゲン化合物を含むガスにさらして、絶縁膜20上に吸着層110を形成する工程と、吸着層110上に金属を含むゲート電極40を形成して、吸着層110とゲート電極40を反応させて、吸着層110をハロゲン含有金属層にする工程とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体装置の製造方法

【課題】素子特性を劣化させることなく、しきい値電圧の低い、金属のゲート電極を有するPチャネルMOSトランジスタを備えた半導体装置を製造することを可能にする。

【解決手段】半導体領域2上にゲート絶縁膜5を形成するステップと、第1金属元素と、OH基、NOx(x=1,2)基のうち少なくとも一つを含有する酸素含有金属層6をゲート絶縁膜上に形成するステップと、酸素含有金属層上に第2金属元素を含むゲート電極膜7を形成するステップと、ゲート電極膜を形成した後、酸素含有金属層の熱分解反応或いは脱水反応が生じる温度以上に加熱するステップと、を備えている。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

半導体装置

【課題】電気的性質が良好なhigh−k膜/Geゲートスタック構造を有する半導体装置を提供する。

【解決手段】Geを主成分とする半導体領域(10)と、前記半導体領域上に形成された絶縁膜(11)と、前記絶縁膜上に形成された金属膜(12)とを具備する半導体装置である。前記絶縁膜は、少なくとも1種の希土類元素(MR)と、TiおよびZrから選択される少なくとも1種のIV族元素(MIV)と、酸素とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】素子分離端における薄膜化を抑制しつつ、第1半導体層と格子定数の異なる第2半導体層を第1半導体層に埋め込む。

【解決手段】Ox、NまたはCの斜めイオン注入16を第1半導体からなる半導体基板11に行うことにより、半導体基板11を構成する第1半導体よりもエッチングレートが小さなエッチブロック層17を素子分離溝12の側壁に形成し、第1半導体よりも格子定数が大きな第2半導体を凹部25内にエピタキシャル成長させることにより、第2半導体からなる埋め込み層26を凹部25内に選択的に形成する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制できるスタティック・ランダム・アクセス・メモリを得ること。

【解決手段】スタティック・ランダム・アクセス・メモリのメモリセルにおける一対のロードトランジスタは、それぞれ、第1のSiGe膜がシリコン基板のソース領域と第1のシリサイド膜との間に存在し、第2のSiGe膜がシリコン基板のドレイン領域と第2のシリサイド膜との間に存在し、前記第1のSiGe膜ならびに前記第2のSiGe膜は、前記前記ソース領域と前記ドレイン領域の間のチャネル領域のシリコン基板の表面よりも低い位置に存在することを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】ゲートパルスストレスによる耐圧劣化およびしきい値電圧の変動を抑制できる半導体装置を提供する。

【解決手段】ゲート電極GEは、ソース領域およびドリフト領域DRに挟まれる領域上に絶縁層FOを介在して形成されている。フィールドプレートFPは、ゲート電極GEおよびドリフト領域DR上を延在し、かつゲート電極GEに電気的に接続されている。ダミー導電層DCは、フィールドプレートFPとドリフト領域DRとの間において絶縁層FO上に形成され、かつソース領域に電気的に接続されている。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上にチャネル長方向が<−110>方向に沿って配置される第1絶縁ゲート型電界効果トランジスタpMOS1と、前記半導体基板上にチャネル長方向が<−110>方向に沿って配置され、前記第1絶縁ゲート型電界効果トランジスタと前記チャネル長方向に隣接する第2絶縁ゲート型電界効果トランジスタnMOS1と、前記第1,第2絶縁ゲート型電界効果トランジスタ上を覆うように設けられ、正の膨張係数を有し、前記第1,第2絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加えピエゾ材料を含む第1ライナー絶縁膜11−1とを具備する。

(もっと読む)

半導体装置とその製造方法

【課題】本発明は、高性能でかつ閾値電圧の低い半導体装置とその製造方法を提供することを目的とする。

【解決手段】基板に形成され、NMOSトランジスタが形成されるNMOS形成領域とPMOSトランジスタが形成されるPMOS形成領域とを絶縁分離する素子分離領域と、該基板上に形成されたHigh−k材料からなるNMOSおよびPMOSのゲート絶縁膜と、該NMOSのゲート絶縁膜上に形成されたNMOSゲート電極と、該PMOSゲート絶縁膜上に形成された第1ニッケルシリサイド層と、該第1ニッケルシリサイド層上に形成され、該第1ニッケルシリサイド層よりも厚くかつ該第1ニッケルシリサイド層よりニッケル密度が大きい第2ニッケルシリサイド層と、を有するPMOSゲート電極と、該NMOSゲート電極および該PMOSゲート電極の側壁に形成されたサイドウォールスペーサとを備える。

(もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】キャップ膜としてのランタン酸化膜の膜厚の増加を抑えつつ、閾値電圧の低減化を図れる、窒化チタン膜を含むメタルゲート電極/Hfを含有するゲート絶縁膜のゲートスタック構造を有するMOSFETを備えた半導体装置を適用すること。

【解決手段】P型半導体領域105を含む半導体基板101と、P型半導体領域101に形成されたNチャネルMOSFETとを具備してなり、前記NチャネルMOSトランジスタは、半導体基板101上に形成され、ハフニウムを含有するゲート絶縁膜108と、ゲート絶縁膜109上に形成され、膜厚が所定値以下のランタン酸化膜109と、ランタン酸化膜109上に形成され、N/Ti原子数比が1未満の窒化チタン膜110を含むゲート電極とを具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】high-k膜とメタルゲート電極とを有する同一導電型の2つ以上のトランジスタが同一基板内に形成された半導体装置において、閾値電圧の差をチャネル領域における不純物濃度の差に由来する閾値電圧の差よりも大きくすることは難しかった。

【解決手段】半導体装置は、第1のトランジスタと、第1のトランジスタと同一導電型の第2のトランジスタとを備えている。第1のトランジスタは、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜8aと、第1のゲート電極11aとを備えている。第2のトランジスタは、高誘電体材料と第1の金属と閾値電圧調整用不純物とを含有する第2のゲート絶縁膜8bと、第2のゲート電極11bとを備えている。第1のゲート絶縁膜8aは、第2のゲート絶縁膜8bに比べて閾値電圧調整用不純物の濃度が低い、又は閾値電圧調整用不純物を含有していない。

(もっと読む)

チャネル半導体合金を備えたトランジスタにおける堆積不均一性の低減によるスレッショルド電圧ばらつきの低減

【解決手段】

シリコン/ゲルマニウム合金のようなスレッショルド調節半導体材質が、高い堆積均一性に基いて1つのタイプのトランジスタに対して選択的に設けられ得る。この目的のために、半導体合金は、任意のトランジスタの能動領域上に堆積させられてよく、そして高度に可制御なパターニングレジームに基いて次いでパターニングされてよい。その結果、スレッショルドばらつきが低減され得る。

(もっと読む)

段階的な形状の構造を有する埋め込み歪誘起材質を伴うトランジスタ

【解決手段】

トランジスタにおいて、段階的な形状のキャビティを設けることによって、シリコン/ゲルマニウム、シリコン/炭素、等のような歪誘起半導体合金がチャネル領域に極めて近接して位置させられてよく、キャビティは次いで歪誘起半導体合金で充填されてよい。この目的で、異なるエッチング挙動の2つ以上の「使い捨て」スペーサ要素が、対応するキャビティの異なる深さで異なる横方向オフセットを規定するために用いられてよい。その結果、高い均一性及びこれに伴い低減されたトランジスタばらつきが、洗練された半導体デバイスに対してさえも達成され得る。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化し、サーマルバジェットの小さなアニールプロセスを用いてトランジスタを作製しても、リーク電流の増大を抑制できる半導体装置を提供すること。

【解決手段】第1導電型の半導体基板上に絶縁膜を介してゲート電極を有し、前記ゲート電極とは絶縁された形で、前記ゲート電極の直下の前記半導体基板のチャネル領域の両側に、第2導電型の不純物がドーピングされたソース・ドレイン領域を有し、前記ソース・ドレイン領域と前記チャネル領域の間に、前記ソース・ドレイン領域と同じ第2導電型であり、前記ソース・ドレイン領域よりも浅く、前記ソース・ドレイン領域と繋がったエクステンション領域を有し、前記エクステンション領域の近傍の第1導電型の領域に、周囲の領域よりも格子欠陥密度の高い高密度欠陥領域が局所的に形成され、前記高密度欠陥領域には、点欠陥が集合した点欠陥集合体が含まれている。

(もっと読む)

141 - 160 / 555

[ Back to top ]