Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

61 - 80 / 555

半導体装置

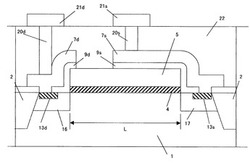

【課題】半導体装置の大きさを大きくすることなく、増幅率の向上と、高耐圧化を図ることを課題とする。

【解決手段】基板上にドレイン部,ゲート部およびソース部が形成され、ゲート部は、基板上に形成されたゲート絶縁膜と、その上に形成されたゲート電極とからなり、ドレイン部は、ゲート電極の一方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ドレイン領域と、より表面近傍に形成された中間濃度ドレイン領域と、基板の上の高濃度ドレイン領域とからなり、ソース部は、ゲート電極の他方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ソース領域と、より表面近傍に形成された中間濃度ソース領域と、基板上の高濃度ソース領域とからなり、高濃度ソース領域は、ゲート電極の上方であって基板表面に平行な方向に延長されたアーム部を備え、アーム部の端部近傍の位置にコンタクト部を有する電極配線部を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOS型トランジスタなどの半導体装置が動作中に生ずる経時的な特性変動を抑制すると共に、高耐圧かつ低オン抵抗が実現される半導体装置およびその製造方法を提供する。

【解決手段】 N型半導体層102に、深さが1μmより小さいP型の第1ドレインオフセット領域103と、深さが第1ドレインオフセット領域103より小さく、不純物濃度が第1ドレインオフセット領域103より大きいP型の第2ドレインオフセット領域105と、第1ドレインオフセット領域103より深いN型のボディ領域106と、N型のソース領域107およびドレイン領域104とを設ける。またLOCOS酸化膜からなる絶縁膜110と、ゲート絶縁膜108を介して形成されたゲート電極109とをN型半導体層102上に備える構造とする。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体領域2と、半導体領域に離間して形成されたソース領域およびドレイン領域12a、12bと、ソース領域12aとドレイン領域12bとの間の半導体領域上に形成され、シリコンと酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、第1絶縁膜と第2絶縁膜との界面7aを含む界面領域7に、Geが導入されており、Geの面密度が、界面領域7内の第1絶縁膜4側においてピークを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧とオン抵抗とのトレードオフ関係を改善する。

【解決手段】ゲート絶縁膜及びLOCOS領域の下、及びドレイン領域を囲むようにドレイン領域に接してオフセット領域を設け、オフセット領域を、第1オフセット領域と、第1オフセット領域の上にドレイン領域を囲み且つLOCOS酸化膜の下に形成される第2オフセット領域と、前記オフセット領域のソース領域側の端部からLOCOSのソース領域側の端部までの間のみに形成される第3オフセット領域とで形成し、第2オフセット領域の不純物濃度を、第1オフセット領域及び第3オフセット領域よりも高くする。高濃度の第2オフセット領域を設けることによりオン抵抗の低減を図り且つ高濃度の第2オフセット領域を低濃度のオフセット領域で挟むことにより、第2オフセット領域の深さ方向の空乏化を促進し電界の緩和を図り耐圧の向上を図る。

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

III族窒化物半導体本体のインシチュドーパント注入及び成長

【課題】半導体材料の構造的及び化学量論的特性を保ったまま、窒化物本体を横方向及び縦方向で空間的に規定された選択ドーピングを達成しうるインシチュドーパント注入及び成長を提供する。

【解決手段】窒化物半導体本体の成長中にインシチュドーパント注入を可能にする方法は、ドーパント注入装置及び成長室を有する複合窒化物室中に、窒化物半導体本体に対する成長環境を確立するステップと、成長室内で窒化物半導体本体を成長させる成長ステップと、ドーパント注入装置を用いて成長室内で窒化物半導体本体にインシチュ状態でドーパント注入を行う注入ステップとを具える。この方法を用いて形成する半導体デバイスは、サポート基板上に形成した第1導電型の窒化物半導体本体と、窒化物半導体本体の成長中にこの窒化物半導体本体のインシチュドーパント注入により形成され、第2導電型を有する少なくとも1つのドープ領域とを具える。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOSトランジスタにおいて、オン抵抗とのトレードオフ関係で最適化されたオフ耐圧を低下させることなく、チャネル長を短くすることによって飽和電流を増加させる。

【解決手段】 チャネルとなる低濃度ボディ領域10と素子分離膜4の間かつゲート酸化膜8の直下に選択的に低濃度ボディ領域10と逆の極性で濃度が高いショートチャネル領域12を設け、ボディ領域10のゲート酸化膜8直下部分のみを高濃度ソース領域7側に後退させた形状を実現する。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積が小さくしかも素子の耐圧の高い半導体装置およびその製造方法を提供する。

【解決手段】基板11と、基板上に設けられた一導電型の第1の半導体層13と、第1の半導体層上に設けられた一導電型で低不純物濃度の第2の半導体層15と、アイソレーション領域50によって分離された素子領域71内に形成されたMOSトランジスタ75と、素子領域内に一主面から第1の半導体層に達して設けられた一導電型で高不純物濃度の領域17と、領域17とMOSトランジスタのドレイン領域35との間に設けられた絶縁領域60であって、一主面10から第1の半導体層13に達し、基板11に達していない絶縁領域60とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】側面に(110)面が形成されたGe若しくはSiGeのフィン構造を実現することができ、FinFET等の素子特性の向上に寄与する。

【解決手段】Ge若しくはSiGeのフィン構造部を有する半導体装置であって、Si基板10の表面部に、一方向に長いストライプ領域を挟むように埋め込み形成され且つ基板表面よりも高い位置まで形成された素子分離絶縁膜12と、ストライプ領域上に形成され、且つ最上面が前記素子分離絶縁膜の最上面よりも低い位置にあるSiGeバッファ層14と、バッファ層14上に形成され、該層14よりも一方向と直交する方向の幅が狭く基板面と垂直な(110)面を有するGeフィン構造16と、を備えた。

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

61 - 80 / 555

[ Back to top ]