Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

21 - 40 / 555

半導体装置及びその製造方法

【課題】配線抵抗を低減することのできる半導体装置を提供する。

【解決手段】一の実施の形態に係る半導体装置は、半導体基板と、半導体基板上にそれぞれ設けられた第1の領域及び第2の領域とを備える。第1の領域は、半導体基板上の第1配線層に形成され、所定の第1の幅を有する第1の金属配線と、第1配線層の上層の第2配線層に形成され第1の幅を有する第2の金属配線と、第1の金属配線と第2の金属配線とを接続し、第1の幅以下の第2の幅を有する第1のコンタクトとを有する。第2の領域は、第1配線層から第2配線層へと亘る膜厚を有し、所定の第3の幅を有する第3の金属配線を有する。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

ターンオン防止付き複合半導体デバイス

【課題】ターンオン防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、ターンオン防止制御を有する複合III-窒化物半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、ノイズを伴う環境内で、ノイズ電流が、ノーマリオンIII-窒化物パワートランジスタのチャネルを通って流れることを防止することによって、ノーマリオフ複合半導体デバイスに、ターンオン防止制御を与えるように構成されている。

(もっと読む)

電界効果トランジスタ及びその製造方法、並びに半導体装置

【課題】横型二重拡散構造を有する電界効果トランジスタの高集積化を可能とする半導体装置を提供する。

【解決手段】半導体装置1Nは、ゲート電極17の幅方向両側のうちの一方の側で延在するP型ボディ領域20Pと、他方の側で延在するN型ボディ領域20Nと、その一方の側に形成されてP型ボディ領域20Pと接合するP型不純物拡散領域32Pと、その他方の側でP型不純物拡散領域32Pと対向する位置に形成されてN型ボディ領域20Nと接合するN型不純物拡散領域32Nと、その一方の側に形成されてP型ボディ領域30Nと接合するN型不純物拡散領域31Nと、その他方の側でN型不純物拡散領域31Nと対向する位置に形成されてN型ボディ領域20Nと接合するP型不純物拡散領域31Pとを備える。

(もっと読む)

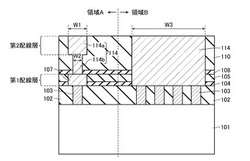

高耐圧電界効果トランジスタ

【課題】高耐圧電界効果トランジスタの素子面積を増大させること無しに、十分に低いオン抵抗を得る。

【解決手段】半導体基板101のn型領域102内に、チャネル形成領域102aを挟んでドレイン低濃度領域103およびソース低濃度領域104を形成し、ドレイン高濃度領域105およびソース高濃度領域106を形成し、ゲート酸化膜109を形成し、該ゲート酸化膜109の端部および低濃度領域103,104を含む領域にフィールド酸化膜110を形成し、さらにゲート酸化膜109からフィールド酸化膜110の端部にかけてゲート電極111を形成した高耐圧pMOSトランジスタにおいて、ゲート電極111とドレイン高濃度領域105との間に、フィールド酸化膜110が形成されていない非酸化領域112を設ける。製造時に、ドレイン低濃度領域103の不純物がフィールド酸化膜110に取り込まれ難くなるので、オン抵抗の増加が抑制される。

(もっと読む)

半導体装置

【課題】MOSトランジスタにおける基板電位をソース領域及びドレイン領域とは異なる電位にすることができ、かつ基板電位の浮きを防止できる半導体装置を提供する。

【解決手段】ゲート電極17に対してチャネル長方向の位置であってチャネル幅方向でドレイン領域11d,11dに挟まれた位置のN型ウェル5によって基板電位用領域11bが形成されている。基板電位用領域11b、基板電位用領域11bよりも濃いN型不純物濃度をもつ基板電位用コンタクト領域9bが形成されている。基板電位用コンタクト領域9bは、基板電位用領域11bとドレイン領域11dのPN接合が所望のPN接合耐圧を得ることができる寸法Lでドレイン領域11dとは間隔をもって配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル層を具備する半導体構造の改良を図ること。

【解決手段】 実施形態の半導体構造は、第1の格子定数を具備する第1の結晶を具備する半導体基板と、前記半導体基板上に形成され、第2の格子定数を具備する第2の結晶を具備する多層エピタキシャル層とを具備している。前記第1の格子定数は、前記第2の格子定数と異なる。前記多層エピタキシャル層は、第1のエピタキシャル層および第2のエピタキシャル層を具備している。前記第1のエピタキシャル層の第1の導電型不純物は、前記第2のエピタキシャル層の第2の導電型不純物よりも少ない。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置

【課題】 高耐圧MOS型トランジスタなどの高耐圧半導体装置における耐圧を向上させ、またドレインオフセット層などの内部電界強度が経時的に変化し、耐圧が変動することを防止する。

【解決手段】 半導体装置、例えば高耐圧MOS型トランジスタは、半導体層2、それと反対導電型の低不純物濃度ソース層3および低不純物濃度ドレイン層4、高不純物濃度ソース層5および高不純物濃度ドレイン層6、厚い絶縁膜8、ゲート絶縁膜9、ゲート電極10を有する。さらにゲート電極10の両側に例えば狭いギャップをもって隣接すると共に電気的フローティングとされた導電性プレート11が厚い絶縁膜8上に設置される。

(もっと読む)

半導体装置

【課題】高耐圧MOS型トランジスタなどの高耐圧半導体装置における耐圧を向上させ、またドレインオフセット層などの内部電界強度が経時的に変化し、耐圧が変動することを防止する。

【解決手段】半導体装置、例えば高耐圧MOS型トランジスタは、半導体層2、それと反対導電型の低不純物濃度ソース層3および低不純物濃度ドレイン層4、高不純物濃度ソース層5および高不純物濃度ドレイン層6、ドレイン側オフセット絶縁膜8a、ソース側オフセット絶縁膜8b、ゲート絶縁膜9、ゲート電極10を有する。ゲート電極10の表面には表面絶縁膜20が形成されており、ドレイン側オフセット絶縁膜8a上の、ゲート電極10と隣接する領域には、少なくとも一部が表面絶縁膜20と接する状態で形成された第1導電性プレート11aが設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

MOSトランジスタおよび半導体集積回路装置の製造方法

【課題】埋込絶縁膜によりゲート絶縁膜の実効的膜厚がドレイン端近傍において増大される構成の高電圧MOSトランジスタにおいて、耐圧特性を劣化させずにオン抵抗を低減させる。

【解決手段】第1導電型の第1のウェル11NW第2導電型の第2のウェル11PWとが形成された半導体基板11と、チャネル領域11CHと、ソースエクステンション領域11aと、第1のウェル11NW中に形成された埋込絶縁膜11Oxと、第2のウェル11PWと埋込絶縁膜11Oxの間に形成されたオフセット領域11offと、埋込絶縁膜11Oxに対してオフセット領域11offとは反対の側に形成された、第1導電型を有するドレインエクステンション領域11bと、チャネル領域11CHとオフセット領域11offおよび埋込絶縁膜11Oxを覆って、ゲート絶縁膜12Gとn+型のポリシリコンゲート電極13Gよりなるゲート電極構造と、を備える。

(もっと読む)

炭化珪素半導体基板、炭化珪素半導体装置、炭化珪素半導体基板の製造方法および炭化珪素半導体装置の製造方法

【課題】高品質な単結晶SiC基板の使用量を減らすことが可能であり、信頼性を向上させることができるSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】支持基板1として、単結晶SiCと異なる材料を用いて構成され、かつ活性層3を形成する工程および半導体素子の構成要素4〜10、14〜17を形成する工程における温度以上の耐熱性を有するものを用い、接合工程では、半導体素子の動作温度以下の温度で直接接合する。このような製造方法では、支持基板1と単結晶SiC基板11とを半導体素子の動作温度以下の温度で接合しているため、支持基板1と単結晶SiC基板11との接合界面で発生する応力を小さくすることができ、SiC半導体装置が使用される際に半導体素子に印加される応力を小さくすることができる。すなわち、SiC半導体装置の信頼性が低下することを抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

マイクロローディング効果を軽減するためのSiGe埋め込みダミーパターンを備えたSiGe装置

【課題】SiGe装置を取り囲んで、SiGeのエピタキシャル成長時にマイクロローディング効果を軽減できるように特別に設計されたSiGe埋め込みダミーパターンを備えた改良されたSiGe装置を提供する。

【解決手段】マイクロローディング効果を軽減するためのダミーパターンを備えた半導体装置は、内部領域200と外部領域400の間に中間環状領域300が設けられた半導体基板1と、基板上、内部領域200に設けられたSiGe装置100と、基板上、中間環状領域300に設けられた複数のダミーパターン20とを含む。複数のダミーパターン20のうち少なくとも1つがSiGeを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

21 - 40 / 555

[ Back to top ]