Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

121 - 140 / 555

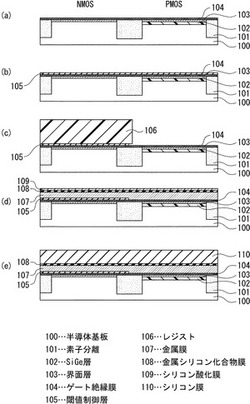

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含むチャネル形成領域を有する電界効果トランジスタにおいて、基板リーク電流を低減する。

【解決手段】半導体装置150は、Geを含む第1導電型の第1の半導体領域101と、第1の半導体領域101上にゲート絶縁膜121を介して形成されたゲート電極122と、第1の半導体領域101におけるゲート電極122の両側方に形成された第2導電型の拡散領域107と、第1の半導体領域101と拡散領域107との間に形成された第1導電型の第2の半導体領域108とを備える。第2の半導体領域108は、第1の半導体領域101におけるゲート電極122下方のチャネル形成領域よりも高い濃度のSiを含有する。

(もっと読む)

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのしきい値電圧制御のために使用する金属酸化膜の膜減り等に起因するしきい値電圧ばらつきを抑制し、所望のしきい値電圧を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、高融点金属酸化物を含む材料からなるゲート絶縁膜3が形成され、ゲート絶縁膜3上に金属酸化膜4が形成される。次いで、金属酸化膜4を構成する金属原子を、金属酸化膜4からゲート絶縁膜3の表面部へ拡散させる処理が実施される。当該金属原子の拡散工程後、上記金属酸化膜4がゲート絶縁膜3に対して選択的に除去される。そして、金属原子が拡散されたゲート絶縁膜3上に導電膜7、8が形成され、当該導電膜7、8を加工することでゲート電極30、31が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル電位固定用のウェル給電用素子を設ける際に、縦型MOSトランジスタ間に素子分離用の埋込絶縁層を必要とせず、素子分離用の埋込絶縁層の形成に必要な面積を削減して、半導体装置の高集積化を図る。

【解決手段】半導体基板1に形成された第1導電型のウェル2内に、ウェル給電用素子Xと縦型MOSトランジスタYとが備えられ、ウェル給電用素子Xは、ウェル2と同じ導電型のボディ領域からなるピラー部P1を有し、ピラー部P1の上部には、第1導電型のウェル2の濃度よりも高い濃度を有する第1導電型の第1不純物拡散層13を備え、縦型MOSトランジスタYは、ウェル2と同じ導電型のボディ領域からなるピラー部P2を有し、かつ縦型MOSトランジスタYのピラー部P2の上部には、第2導電型の第2不純物拡散層7を備えることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】電界集中が発生しにくく、信頼性の高い耐圧構造を有する半導体装置を提供すること。

【解決手段】p基板10の表面層にNwell層9を形成し、Nwell層9の表面層にn形の高電位領域8、p形の低電位領域12およびPoffset領域14を形成し、p基板10の表面側には、絶縁酸化膜18を介して、第1導電形薄膜層4と第2導電形薄膜層5の繰り返しからなる渦巻き状薄膜層6を複数形成し、p基板10の裏面側には、裏面側電極11を形成する。この構造において、低電位側電極3を基準にして、高電位側電極2に正電位VS を印加すると、渦巻き状の薄膜層6の高電位側電極2と接続する端にも電位VS が印加され、この渦巻き状の薄膜層には均一な電位分布が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】希土類含有複合酸化物膜の新規なエッチング方法を含む、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、希土類元素と、希土類でない他の金属元素と、Oとを含む希土類含有複合酸化物膜を形成する工程と、希土類含有複合酸化物膜に対し、フッ素を含まない酸によるエッチングと、他の金属元素の酸化物を溶解するフッ素含有溶液によるエッチングとを、交互に複数回行なうエッチング工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

半導体装置

【課題】SiGeのチャネルを有する半導体装置の高性能化及び高信頼化をはかる。

【解決手段】シリコンを主成分とする半導体基板101の一主面に設けられ、素子分離絶縁膜102によって区画された素子形成領域103と、チャネル領域となるSi及びGeを主成分とし素子形成領域103上に設けられた半導体膜104と、半導体膜104上にゲート絶縁膜105を介して設けられたゲート電極106と、チャネル領域を挟んで半導体膜104及び基板101に形成されS/D領域110と、ゲート電極106の両側面に設けられた側壁絶縁膜109と、S/D領域110上の側壁絶縁膜109で区画されたS/Dコンタクト領域上に半導体膜104と金属との反応により形成され、且つS/Dコンタクト領域以外の半導体膜104よりも薄い膜厚に形成された金属化合物膜111とを備えた。

(もっと読む)

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

電界効果トランジスタのソース延長部及びドレイン延長部が異なるドーパントで画定される半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられた絶縁ゲート電界効果トランジスタ(100)は、チャンネルゾーン(244)によって横方向に分離された一対のソース/ドレインゾーン(240及び242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーン上方でゲート誘電体層(260)の上側に存在している。各ソース/ドレインゾーンは、主要部分(204M又は242M)及び該主要部分と横方向に連続的であり且つ該ゲート電極下側を横方向に延在する一層軽度にドープした横方向延長部(240E又は242E)を包含している。該横方向延長部は、該チャンネルゾーンを上部半導体表面に沿って終端させており、異なる原子量の一対の半導体ドーパントによって夫々ほぼ画定される。該トランジスタが非対称的装置であり、該ソース/ドレインゾーンはソース及びドレインを構成する。該ソースの横方向延長部は該ドレインの横方向延長部よりも一層軽度にドープされており且つ一層高い原子量のドーパントで画定される。

(もっと読む)

半導体装置およびその製造方法

【課題】大きな歪み量を発生可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、CとCの濃度の10倍以上のGeとを含んだSiGeC層を形成する工程(S3)と、SiGeC層内のCのうちで格子置換位置に位置しているものを格子間位置へと移動させることによって、前記SiGeC層内の全てのCに対する格子置換位置に位置するCの割合を形成された時点での割合から低下させて50%以下に低下させる工程(S4)と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル特性を低下させることなく、チャネル領域に十分な歪みを生じさせることのできる半導体層が埋め込まれたソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】N型のシリコン基板11の主面にゲート絶縁膜を介して形成されたゲート電極13と、ゲート電極13の下方に形成されるチャネル領域14を挟むように形成され、チャネル領域14に歪みを与えるためのゲルマニウム、P型不純物のボロンおよびボロンの拡散を抑制するためのカーボンを含有する第1半導体層15a、15bと、ゲルマニウムおよびボロンを含有する第2半導体層16a、16bと、が順に積層された構造を有するソース・ドレイン領域17a、17bと、第2半導体層16a、16bのゲート電極13側の側面からチャネル領域14に隣接するエクステンション領域18a、18bと、を具備する。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

複数の局所的濃度最大によって画定されたソース/ドレイン延長部を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(100W)は、半導体ボディのボディ物質(180)のチャンネルゾーン(244)によって横方向に分離されているソース(980)及びドレイン(242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーンの上方でゲート誘電体層(260)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250)が、通常、該ソースのみにほぼ沿って延在しており、従って該IGFETは非対称的装置である。該ソースを画定する半導体ドーパントはソース延長部を画定する場合に複数の局所的濃度最大に到達する。2つのこの様な局所的濃度最大に到達する半導体ドーパントで該ソース延長部を画定する場合に関与する手順は、3個の絶縁ゲート電界効果トランジスタ用の相互に異なる特性のソース/ドレイン延長部を2つのソース/ドレイン延長部ドーピング操作のみで画定することを可能とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電界効果型トランジスタの動作速度を向上させる半導体装置の製造方法、及び半導体装置を提供する。

【解決手段】 ゲルマニウム基板の上にシリコンゲルマニウムを含むエピタキシャル成長層を形成する工程と、エピタキシャル成長層上に酸化物層を形成する工程と、エピタキシャル成長層を熱処理する熱処理工程と、を含み、熱処理工程における熱処理は、加熱温度が600℃以上900℃以下であり、ゲルマニウム基板の上にシリコンゲルマニウムからなるエピタキシャル成長層を形成する工程は、エピタキシャル成長層にシリコンが5%以上20%以下、及びゲルマニウムが80%以上95%以下の割合で含有するように形成する。

(もっと読む)

121 - 140 / 555

[ Back to top ]