Fターム[5F140AC32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 用途 (713) | メモリ (556)

Fターム[5F140AC32]に分類される特許

121 - 140 / 556

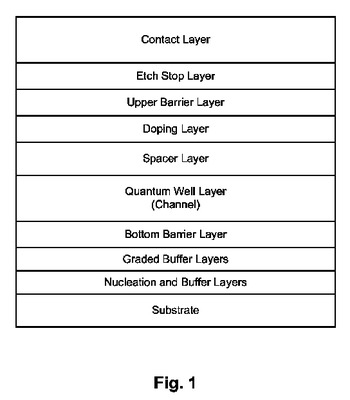

非平面ゲルマニウム量子井戸デバイス

非平面(ノンプレーナ)ゲルマニウム量子井戸構造を形成する技術が開示される。量子井戸構造は、IV族又はIII−V族の半導体材料を用いて実現されることができ、ゲルマニウムフィン構造を含む。一例において、非平面量子井戸デバイスが提供され、このデバイスは、基板(例えば、シリコン上にSiGe又はGaAsのバッファを有する)と、IV族又はIII−V族材料のバリア層(例えば、SiGe、GaAs又はAlGaAs)と、ドーピング層(例えば、デルタ/変調ドープされる)と、アンドープのゲルマニウム量子井戸層とを有する量子井戸構造を含む。アンドープのゲルマニウムフィン構造が量子井戸構造内に形成され、該フィン構造上に頂部バリア層が堆積される。ゲートメタルが、フィン構造を横切って堆積される。ドレイン/ソース領域がフィン構造のそれぞれのエンドに形成され得る。  (もっと読む)

(もっと読む)

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを備えた半導体装置において、トランジスタのGIDLを抑制する。

【解決手段】縦型トランジスタを備えた半導体装置に関する。縦型トランジスタは、半導体領域と、半導体領域上に設けられた柱状領域と、柱状領域の側面を覆うように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、柱状領域の上部に設けられた第1の不純物拡散領域と、半導体領域内に柱状領域を囲むように設けられた第2の不純物拡散領域と、を有する。第1の不純物拡散領域は、柱状領域の側面と離間するように設けられている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

半導体装置、半導体チップ及び半導体装置の製造方法

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法、半導体装置及びデータ処理システム

【課題】第1配線の比抵抗が小さく、シリサイド異常成長が抑制された半導体装置の製造方法の提供。

【解決手段】第1溝を半導体基板1に設けた後、第1溝内に、シリコンとの間でシリサイドを形成しない材料からなる導体層6と半導体層10とを含む第1配線11を形成して、半導体層と半導体基板とを直接に接触させる工程と、半導体層に含まれるドーパントを半導体基板に拡散させて第1不純物拡散領域13を形成する工程と、第1溝と交差する方向に延在する第2溝を半導体基板に設けることで、第1不純物拡散領域を包含して半導体基板に立設されたピラー部1bを形成する工程と、第2溝の側壁面にゲート絶縁膜16を形成してから、ゲート絶縁膜を介してピラー部に対向する第2配線17を第2溝内に形成する工程と、ピラー部の先端部に、第2不純物拡散領域19を形成する工程と、を具備してなる半導体装置の製造方法を採用する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】駆動電流の増大を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に線状に形成された第2部分12bと、を有する第2半導体層12と、前記第2半導体層の前記第2部分の周囲に絶縁膜17を介して形成されたゲート電極18と、を具備し、前記第2半導体層の前記第2部分の膜厚は、前記第2半導体層の前記第1部分の膜厚より小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】プログラム後の誤読み出しを抑制でき、高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1上のチャンネル領域に形成されたゲート酸化膜3と、前記ゲート酸化膜3上に形成されたゲート電極4と、前記チャンネル領域の少なくとも一部に形成されたシリサイド層2と、を有し、前記シリサイド層2は、前記チャンネル領域のうち前記ゲート電極4の全体を除く領域の少なくとも一部を被覆する。

(もっと読む)

121 - 140 / 556

[ Back to top ]