Fターム[5F140AC32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 用途 (713) | メモリ (556)

Fターム[5F140AC32]に分類される特許

81 - 100 / 556

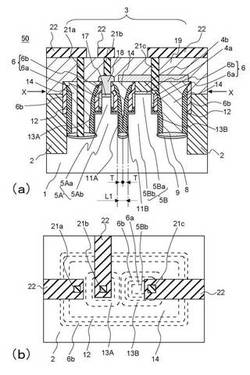

半導体デバイス及びその製造方法

【課題】ゲート電極と上部導電層とのショートを防止した安定動作可能な縦型MOSトランジスタを有する半導体デバイスを提供する。

【解決手段】縦型MOSトランジスタを構成する半導体ピラー5Aは、第1の幅を有する上部5Aaと第2の幅を有する下部5Abを有し、上部5Aa側面は第2の絶縁膜6aと第3の絶縁膜6bで覆われ、下部5Abは側面から第2の絶縁膜6aまでゲート絶縁膜である第1の絶縁膜11Aで覆われており、ゲート電極13Aが第2及び第3の絶縁膜6により上部導電層18と絶縁されている。

(もっと読む)

Zr−Ge−Ti−OまたはHf−Ge−Ti−Oの誘電材料を備えた物質とその製造方法

【課題】 フィルム、またはRがZrとHfから選択されたR−Ge−Ti−Oを備えた誘電材料とその製造方法を提供する。

【解決手段】 本発明は、RがZrとHfから選択される、R−Ge−Ti−Oのフィルムを備えた誘電材料に関し、また、その製造方法に関連する。誘電材料は、公式Rx−Gey−Tiz−Owを有することが好ましく、ここで、.05≧x≦1、.05≦y≦1、0.1≧z≦1、1≧w≦2、x+y+z≡1であり、さらに好ましくは、0.15≧x≦0.7、.05≧y≦0.3、0.25≧z≦0.7、1.95≧w≦2.05であり、x+y+z≡1である。本発明は、ダイナミック・ランダム・アクセス・メモリ(DRAM)装置のコンデンサを備えたシリコンチップ集積回路装置での使用に特に有用である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、素子面積を縮小可能で高耐圧なMOS型電界効果トランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】

本実施形態の半導体装置100は、半導体基板10と、半導体基板10に設けられた素子分離領域14a,14bと、隣接する素子分離領域で区画された素子領域上に半導体基板10上に設けられたゲート絶縁膜12と、ゲート絶縁膜12上に設けられたゲート電極13と、ゲート電極13の直下近傍の素子領域表面に設けられたソース・ドレイン拡散領域11a,11bと、前記ソース・ドレイン拡散領域11a,11b上に設けられたコンタクトプラグ15a,15bとを備え、ゲート絶縁膜12のドレイン側の膜厚は、ゲート絶縁膜12のソース側の膜厚より厚いことを特徴とする。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域のトランジスタにおけるソース/ドレイン電極上の半導体層同士の接触による短絡を防止しつつ、周辺回路領域のトランジスタにおけるせり上げソース/ドレイン領域を含むソース/ドレイン電極の高濃度不純物層の接合深さの均一性を図り、短チャネル効果を抑制する。

【解決手段】メモリセル領域における隣接するトランジスタ間で半導体層同士が接触しない膜厚にエピタキシャル成長させ、その際、周辺回路領域の素子分離2のみを後退させて露出した基板面からもエピタキシャル成長半導体層10を成長させることで、周辺回路領域の半導体層のファセットFが活性領域外に形成されるようにし、その後、周辺回路領域に高濃度不純物層11用のイオン注入を行う。

(もっと読む)

半導体装置の製造方法

【課題】溝内の一部のみを覆うマスクパターンを、フォトレジスト膜を用いて形成する必要のない半導体装置の製造方法を提供する。

【解決手段】半導体基板1に、第1溝7を形成する工程と、第1溝7に第1絶縁膜8を形成する工程と、上面が第1絶縁膜の上端よりも下方になるように第1溝7内に第1導電膜9を充填する工程と、第1溝7の側面にカーボン膜10を形成する工程と、第1溝7内を第2絶縁膜11で充填する工程と、第1溝7内の側面の一方を覆うカーボン膜10を除去し、第1絶縁膜8の一部を露出させる工程と、第2絶縁膜11と露出された第1絶縁膜8を除去し、半導体基板1の一部を露出する工程と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーシリコンピラーを用いてゲート電極を延長する場合の、シリコンピラーにおける反り変形の発生を抑制する。

【解決手段】半導体装置の製造方法は、第1及び第2のシリコンピラー3,4の側周面3a,4aに形成されたゲート絶縁膜9を覆うゲート電極材料を成膜する工程を備え、ゲート電極材料の成膜量は、ゲート絶縁膜9を介して側周面3aを覆う第1の部分と、ゲート絶縁膜9を介して側周面4aを覆う第2の部分とが接触しないよう制御され、第1及び第2の部分を覆うとともに第1の部分と第2の部分の間の領域を埋めるマスク絶縁膜を形成する工程と、マスク絶縁膜をマスクとして用いてゲート電極材料をエッチングすることにより、ゲート絶縁膜9を介してそれぞれ側周面3a,4aを覆うゲート電極101,102と、ゲート電極101,102とを電気的に接続する導体膜11とを形成する工程とをさら備える。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

81 - 100 / 556

[ Back to top ]