Fターム[5F140BA07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | GaAs (412)

Fターム[5F140BA07]に分類される特許

101 - 120 / 412

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタを提供する。

【解決手段】本発明は、フィン型電界効果トランジスタの分離構造に関する。フィン型電界効果トランジスタの例は、主表面からなる基板と、基板の主表面から突出する複数のフィン構造と、フィン構造の間に位置する複数の分離構造と、からなる。各フィン構造は、変化位置により分けられる上部分と下部分からなり、この変化位置は、フィン構造の側壁と基板の主表面の角度85度のところにあり、上部分は、この基板の主表面と実質上、垂直な側壁、及び、第一幅を有する頂面を有し、下部分は、上部分の両側のテーパ型側壁、及び、第一幅より大きい第二幅を有する底部を有する。複数の分離構造は、それぞれ、基板の主表面から、変化位置上の点に延伸する。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

成膜方法及び処理システム

【課題】スループットを高く維持しつつリーク電流を抑制してリーク特性も高く維持することが可能な成膜方法を提供する。

【解決手段】被処理体の表面とゲート電極との間に介在されるゲート絶縁層を形成する成膜方法において、シリコンを含む界面膜を所定の温度で形成する界面膜形成工程S1と、被処理体を冷却する冷却工程S2と、冷却された被処理体に対して界面膜形成工程の所定の温度より低い温度でゲート絶縁膜を形成するゲート絶縁膜形成工程S3とを有する。

(もっと読む)

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

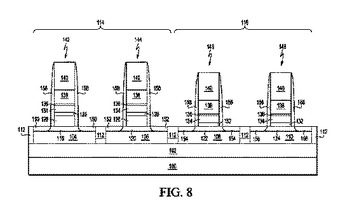

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

集積回路構造及びその製造方法

【課題】 非対称的なソース及びドレイン領域を有する構造を提供する。

【解決手段】 本発明の方法は、少なくとも1つの半導体チャネル領域を有する基板と、半導体チャネル領域を覆うように基板の上面に設けられたゲート誘電体層と、ゲート誘電体層上のゲート導電体とを有する構造を形成する。非対称的な側壁スペーサがゲート導電体の側壁に配置され、そして非対称的なソース及びドレイン領域が半導体チャネル領域に隣接して基板内に配置される。ソース及びドレイン領域の一方は、他方よりもゲート導電体の中心に近づけられる。ソース及びドレイン領域は、半導体チャネル領域に物理的な応力を与える材料で構成される。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTを小さく保ちつつ、より高い実効仕事関数を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101のn型活性領域103の上に形成された第1のゲート絶縁膜107と、第1のゲート絶縁膜107の上に形成された第1のゲート電極111とを有している。第1のゲート絶縁膜107は、ハフニウム及びアルミニウムを含み、且つ中央部において上部及び下部よりもアルミニウムの濃度が高い。第1のゲート電極111はチタンを含む。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に第1窒化物半導体層、第2窒化物半導体層、および第3窒化物半導体層が順次積層された窒化物半導体積層体と、ソース電極およびドレイン電極と、第2窒化物半導体層および第3窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域の内面および窒化物半導体積層体の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含み、絶縁膜に接する第1窒化物半導体層の上面と、第2窒化物半導体層に接する第1窒化物半導体層の上面とに段差がないことを特徴とする。

(もっと読む)

電磁気素子の製造方法

【課題】レジスト残渣に起因するリーク電流の増大を生じさせることがなく、微細パターンの形成が可能であり、電極のエッジ部分の絶縁膜が薄くなることに起因するリーク電流の増大を抑制することが可能な電磁気素子の製造方法を提供すること。

【解決手段】基板上に、12(CaxSr1-x)O・7Al2O3(0≦x≦1)を含む絶縁膜を形成する絶縁膜形成工程と、絶縁膜の上にアンモニウム塩アルカリ溶液を含む現像液で現像可能な第1フォトレジストを塗布し、第1フォトマスクパターンに応じて第1フォトレジストを露光する第1フォトレジストパターン形成工程と、第1フォトレジストをアンモニウム塩アルカリ溶液を含む現像液に接触させ、第1フォトレジストの可溶部分の溶解と同時に、絶縁膜をエッチングする現像・エッチング工程とを備えた電磁気素子の製造方法。

(もっと読む)

高移動度マルチゲートトランジスタのフィン構造

【課題】 半導体トランジスタの垂直フィン構造及びその製造方法を提供する。

【解決手段】 半導体トランジスタの垂直フィン構造であって、半導体基板、この半導体基板の上部のフィン層、及びこのフィン層を覆うキャッピング層を含み、半導体基板は、IV族半導体材料を含み、フィン層は、IV族半導体材料を含み、キャッピング層は、III−V族半導体化合物を含み、フィン層は、半導体トランジスタのチャネルとなり、キャッピング層は、フィン層に歪みを加え、チャネルを通過する移動度を向上させる垂直フィン構造。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

電磁気素子用絶縁膜及び電界効果素子

【課題】リーク電流を増大させることなく薄膜化が可能であり、素子を微細化することができ、しかも、界面準位に起因する動作の不安定化を生じるおそれが少ない電磁気素子用絶縁膜、及び、このような電磁気素子用絶縁膜を用いた電界効果素子を提供すること。

【解決手段】12(CaxSr1-x)O・7Al2O3(0≦x≦1)で表される組成を有し、アモルファス構造を備えた電磁気素子用絶縁膜。半導体Aと、半導体A上に形成されたソース電極S及びドレイン電極Dと、ソース電極S−ドレイン電極D間の通電方向に対して垂直方向に電界を印加するためのゲート電極Gと、半導体Aとゲート電極Gとの間に形成されたゲート絶縁膜Bとを備えた電界効果素子10。ゲート絶縁膜Bは、本発明に係る電磁気素子用絶縁膜からなる。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

傾斜三元または四元マルチゲートトランジスタ

【課題】 フィン電界効果トランジスタ(FinFET)とその形成方法を提供する。

【解決手段】 半導体基板、前記半導体基板上の絶縁領域、及び前記半導体基板上に位置し、前記絶縁領域間の間隙に少なくとも一部を有し、第1III-V族化合物半導体材料を含むエピタキシー領域を含み、前記エピタキシー領域は、そこと前記半導体基板が第1格子不整合を有する下部分、及び前記下部分上に位置し、そこと前記半導体基板が前記第1格子不整合と異なる第2格子不整合を有する上部分を更に含む集積回路構造。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

101 - 120 / 412

[ Back to top ]