Fターム[5F140BA07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | GaAs (412)

Fターム[5F140BA07]に分類される特許

41 - 60 / 412

半導体装置の製造方法及び半導体基板の洗浄方法

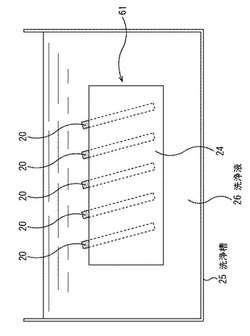

【課題】半導体基板の洗浄をより効率的に行うことができる半導体装置の製造方法及び半導体基板の洗浄方法等を提供する。

【解決手段】半導体基板20をその主面を鉛直方向及び水平方向から傾斜させて保持し、酸を含む洗浄液26に半導体基板20を浸漬する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】閾値変動を抑えつつ、ゲートリーク電流を低減させた窒化物半導体HEMT。

【解決手段】窒化物系半導体で形成された半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を備え、ゲート絶縁膜は、酸窒化膜で形成された第1絶縁膜と、タンタル、ハフニウム、ハフニウムアルミニウム、ランタン、およびイットリウムの少なくとも1つを含む第2絶縁膜と、を有する半導体装置を提供する。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】界面準位密度のゲート酸化膜/半導体界面が形成された半導体装置、および作製方法の提供。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置とする。シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜(あるいは酸化膜)-半導体(MISあるいはMOS)構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図る。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Si3N4の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

41 - 60 / 412

[ Back to top ]