Fターム[5F140BA07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | GaAs (412)

Fターム[5F140BA07]に分類される特許

141 - 160 / 412

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

絶縁膜、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合でもSBDやSILCが生じ難く、高い絶縁破壊耐性(SILC、TZDB、TDDBの改善)が得られる絶縁膜、それを用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】主として半導体材料で構成された半導体基板2に接触して設けられ、シリコン、酸素原子、および、これらの原子以外の少なくとも1種の原子Xを含有する絶縁性無機材料を主材料として構成され、水素原子を含むゲート絶縁膜3であって、その厚さ方向の少なくとも一部において、前記原子Xの総濃度をAとし、前記水素原子の濃度をBとしたとき、B/Aが10以下なる関係を満足する領域を有している。これにより、薄膜化した場合でもSBDやSILCが生じ難く、高い絶縁破壊耐性を得ることができる。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

半導体装置

【課題】高周波高出力増幅に用いるFETを具えた半導体装置において、交差部に起因の寄生容量を防止し、かつチップ面積を拡大せずに発熱の集中を分散させる。

【解決手段】半導体装置は、ゲート幅方向15に互いに平行にかつ離間して形成されている複数のゲート電極13と、ゲート長方向11に延在して形成されている基線部17と、複数の主電極19とが下地21の上側に設けられている。ゲート電極は、基線部とそれぞれ交差し、かつこの基線部と一体的に形成されている。主電極は、基線部、及び隣り合うゲート電極の間に囲まれた領域に1つずつ配置形成されている

(もっと読む)

半導体装置

【課題】ノーマリオフ特性が実現され、飽和電流値低下が生じず、ゲート電圧に対するドレイン・ソース間電流特性が良好なHEMTを実現する半導体装置を提供する。

【解決手段】第1半導体層131と、第1半導体層131の主面135上に積層され、第1半導体層131の主面135側に2DEG層137を生じさせる第2半導体層133と、第1半導体層131及び第2半導体層133と比して電子親和力χが大きい半導体材料からなり、2DEG層137と電気的に接続された第3半導体層139と、第2半導体層133及び第3半導体層139上に設けられた絶縁膜157と、第3半導体層139にオーミック接続される第1電極151と、第2半導体層133及び第3半導体層139上に絶縁膜157を介して設けられた第2電極153と、第1電極151との間に第2電極153を介在させ、2DEG層137と電気的に接続された第3電極155とを備える。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

【課題】本発明はトレンチの上部縁部位でゲート絶縁膜が薄くなる現象を防止し、均一な厚さを有するゲート絶縁膜を形成することができる半導体素子、およびその製造方法を提供する。

【解決手段】本発明の半導体素子は、活性領域を画定するトレンチが形成された基板と、該トレンチに埋め込まれた素子分離膜と、前記活性領域上にゲート絶縁膜の成長時に前記トレンチの上部縁部位での酸化を促進するために前記トレンチの上部縁部位に形成された酸化促進領域と、ゲート絶縁膜上に形成されたゲート導電膜と、を備える。

(もっと読む)

ゲイン変化補償を伴うトランジスタ

半導体装置(10)およびこれを製造方法は、活性素子領域(12)および隔離領域(14)を提供する工程を含み、隔離領域は、活性素子領域との境界(32)を形成する。パターン化ゲート材料(16)は、境界の第1部分(34)と第2(36)部分との間において、活性素子領域と重なる。パターン化ゲート材料は、活性素子領域内において、チャネルを画定し、ゲート材料は、境界領域の第1部分および第2部分の付近において、境界の第1部分と第2部分との間よりも大きい(24+26,28+30)、ゲート材料の主要寸法に沿って中心線(18)と直交するゲート長さ寸法を有する。チャネルは、境界の第1部分に隣接する第1端と、境界の第2部分に隣接する第2端とを含み、更に、チャネルの両端においてテーパが付けられたゲート長さ寸法によって特徴付けられる。  (もっと読む)

(もっと読む)

半導体デバイス

【課題】エンハンスメントモードトランジスタを作製する方法を提供する。

【解決手段】基板1上の第1活性層3と、第1活性層3の上に、該第1活性層3に比較して高いバンドギャップを有する第2活性層4配設し、実質的にGaを含まないで少なくともAlを含む第2活性層4と、第2活性層4の少なくとも一部の上のゲート絶縁層5であって、第2活性層4の少なくとも一部を熱酸化して形成されたゲート絶縁層5と、ゲート絶縁層5の少なくとも一部の上のゲート電極6と、第2活性層4の上のソース電極7およびドレイン電極8とを含み、前記半導体デバイス10は、更に、動作時でゲート電極6とソース電極7が同電圧の場合、第1活性層3と第2活性層4の間で、ゲート電極6の外側でゲート電極6の位置以外に、2次元電子ガス2DEG層を含む。

(もっと読む)

窪み付きゲート構造を有するメモリデバイス及びその製造方法

【課題】本発明は、IC(integrated circuit)の集積度が向上し、しかもショートチャネル効果を防止することができるMOS半導体デバイスを形成する方法を提供する。

【解決手段】DRAMアクセストランジスタのようなメモリデバイスであって、窪み付きゲート構造を有するメモリデバイスを形成する方法が開示されている。まず、絶縁用のフィールド酸化物領域(21)が半導体基板上に形成され、ついで、窒化シリコン層(18)にパターン形成が行われ、エッチングによりトランジスタトレンチ(22)が得られる。その後にデポジットされたポリシリコンであって、ゲート構造形成のためのポリシリコンを、隣接し隆起した窒化シリコン構造に対して研磨できるようにするため、このトランジスタトレンチに隣接するフィールド酸化物領域に窪みが設けられる。

(もっと読む)

半導体装置及び電子機器

【課題】面積を増大させることなく、過電圧に対する耐性を高めることを課題の一つとする。

【解決手段】第1の端子部100に設けられ、第1のn型不純物領域106と、平面視において前記第1のn型不純物領域106の内周部に設けられた第1の抵抗領域107と、平面視において前記第1の抵抗領域107の内周部に設けられた第1のp型不純物領域108と、を有する第1の半導体領域103と、前記第2の端子部101に設けられ、第2のp型不純物領域109と、平面視において前記第2のp型不純物領域109の内周部に設けられた第2の抵抗領域110と、前記第2の抵抗領域110の内周部に設けられた第2のn型不純物領域111と、を有する第2の半導体領域104と、有する構成である。

(もっと読む)

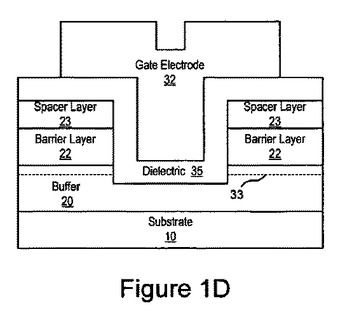

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

小型化可能な量子井戸デバイスおよびその製造方法

【課題】小型化可能な、量子井戸デバイスおよびその製造方法を提供する。

【解決手段】量子井戸QWデバイスは、基板1を覆う量子井戸領域QW、量子井戸領域の一部を覆うゲート領域G、ゲート領域に隣接するソース領域Sおよびドレイン領域Dを含む。量子井戸領域は、第1バンドギャップを有する半導体材料を含むバッファ構造2と、バッファ構造2を覆い、第2バンドギャップを有する半導体材料を含むチャネル構造3と、チャネル構造3と接する第3バンドギャップを有するアンドープの半導体材料を含むバリア構造4とを含み、第1バンドギャップと第3バンドギャップは、第2バンドギャップより広い。ソース領域Sとドレイン領域Dは、それぞれゲート領域Gに対してセルフアラインであり、第4バンドギャップを有する半導体材料を含み、第4バンドギャップは第2バンドギャップより広い。

(もっと読む)

半導体装置

【課題】 スナップバック現象が発生する時のドレイン電流値を大きくすることによって、ESD耐量を改善する。

【解決手段】 半導体装置10は、ソース領域23とボディ領域21の間の少なくとも一部に絶縁領域22を備えている。絶縁領域22は、ソース領域23とボディ領域21とドリフト領域25で構成される寄生のnpnトランジスタのベース・エミッタ間の接合面積を小さくするので、寄生のnpnトランジスタがオンした後にソース領域23から注入される電子量を低減する。これにより、スナップバック現象が発生する時のドレイン電流値を大きくすることができる。

(もっと読む)

半導体装置

【課題】ゲート電極の構造が異なる2種類のトランジスタを形成する際のゲート絶縁膜の突き抜け及び基板掘れが生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の第1の領域13に形成された第1のトランジスタ20と、第2の領域14に形成された第2のトランジスタ30とを備えている。第1のトランジスタ20は、第1のゲート絶縁膜21と、第1のゲート電極22とを有し、第2のトランジスタ30は、第2のゲート絶縁膜31と、第2のゲート電極32とを有している。第1のゲート絶縁膜21及び第2のゲート絶縁膜22は、第1の絶縁膜41と第2の絶縁膜42とを含む。第1のゲート電極22に含まれる元素と、第2のゲート電極32に含まれる元素とは少なくとも一部が異なっている。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

141 - 160 / 412

[ Back to top ]