Fターム[5F140BA07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | GaAs (412)

Fターム[5F140BA07]に分類される特許

161 - 180 / 412

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧の半導体装置の耐圧を低下させることなく寸法を縮小することを課題とする。

【解決手段】半導体基板上に形成したリサーフ領域を含むドレインドリフト領域を備える半導体装置であり、ドレインドリフト領域がゲート長方向に波型(ウェーブ)状の下面形状を有することにより上記課題を解決する。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

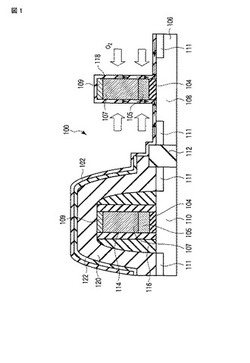

二重仕事関数半導体デバイスの製造方法及びそのデバイス

【課題】金属ゲート電極を有する二重仕事関数半導体デバイスの製造方法を提供する。

【解決手段】該製造方法は、第1領域101及び第2領域102を有する基板100を設けること、第1領域に第1半導体トランジスタ107を作製すること、第2領域に第2半導体トランジスタ108を作製すること、第1サーマルバジェットを第1半導体トランジスタに備わる少なくとも第1ゲート誘電体キャッピング層114aに作用し、第2サーマルバジェットを第2半導体トランジスタに備わる少なくとも第2ゲート誘電体キャッピング層114bに作用すること、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ開口部の緩やかな傾斜部の角度ゆらぎを低減することを課題とする。

【解決手段】半導体基板上の素子領域上にトレンチエッチマスクを形成する工程と、前記トレンチエッチマスクを用いて、前記半導体基板をエッチングすることで、第1の傾斜部を有する第1の溝を形成する工程と、前記トレンチエッチマスクの側壁と、前記第1の傾斜部の少なくとも一部を覆うサイドウォールスペーサーを形成する工程と、前記トレンチエッチマスクとサイドウォールスペーサーとを用いて、前記半導体基板をエッチングし、前記第1の傾斜部より急な第2の傾斜部を有する第2の溝を形成する工程を経ることで、第1の傾斜部と第2の傾斜部とから構成されるトレンチを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することを可能にする。

【解決手段】配列された複数の素子形成領域AR1を含むp型半導体層103における隣り合う素子形成領域AR1間に平行な2つの溝TRを形成し、個片化時には2つの溝TRの間に形成された凸部120を切断する。この構成により、スクライブ領域SR全体に溝TRを形成する必要が無くなるため、溝TRの幅を例えばダイシングブレードの厚さやレーザスポットの径よりも小さくすることが可能となる。この結果、微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することが可能となる。

(もっと読む)

半導体基板、半導体基板の製造方法および半導体装置

【課題】半導体−絶縁体界面の界面準位が低減した半導体基板とその製造方法および半導体装置を提供する。

【解決手段】砒素を含む3−5族化合物の半導体層と、酸化物、窒化物または酸窒化物の絶縁層と、を備え、前記半導体層と前記絶縁層との間に砒素の酸化物が検出されない半導体基板が提供される。当該第1の形態において半導体基板は、前記半導体層と前記絶縁層との間に存在する元素を対象としたX線光電子分光法による光電子強度の分光観察において、砒素に起因する元素ピークの高結合エネルギー側に、酸化された砒素に起因する酸化物ピークが検出されないものであってよい。

(もっと読む)

電界効果トランジスタの製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を活性化することができるIII族半導体材料電界効果トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる電界効果トランジスタの製造方法は、基板やサンプルステージ等を加熱しこれらの熱伝導を用いて半導体層を昇温することによって不純物を活性化させるのではなく、キャリア移動層を形成するGaN層103のバンドギャップエネルギーよりも高いエネルギーを有する波長の紫外線レーザ光Lを照射することによって電界効果トランジスタの構成層に含まれる不純物を活性化させるため、デバイスの性能や信頼性を低下させることなく、注入した不純物を活性化することができる。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極下端の側面に接する領域に半導体表面が露出することを防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板(20)の上に、電子走行層(21)と電子供給層(23)とが配置されている。電子供給層の上に、ソース電極(30F)及びドレイン電極(31F)が、相互に間隔を隔てて配置されている。ソース電極とドレイン電極との間の電子供給層の上に、ゲート電極(40F)が配置されている。電子供給層の上に、ソース電極とゲート電極との間の領域、及びドレイン電極とゲート電極との間の領域を覆う保護膜(35)が形成されている。ゲート横開口(38)が保護膜に形成されている。ゲート横開口は、ソース電極とゲート電極との間の領域、及びドレイン電極とゲート電極との間の領域の少なくとも一方に、ゲート電極、ソース電極、及びドレイン電極のいずれからも間隔を隔てて配置されている。

(もっと読む)

トリゲート・デバイス及び製造方法

【課題】 基板上に形成された上面及び左右両側の側壁を備えた半導体ボディを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 ゲート誘電体層が、半導体ボディの上面上及び半導体ボディの左右両側の側壁上に形成される。ゲート電極は、半導体ボディの上面上のゲート誘電体上に形成されると共に、半導体ボディの左右両側の側壁上のゲート誘電体に隣接して形成される。

(もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

制御された結晶構造を用いた、ドーパント及び多層シリコン膜の使用による多結晶シリコン膜及び周囲層の応力の調節

【課題】応力を調整した多層シリコン膜を形成する方法を提供する。

【解決手段】シリコンソースガスを備える第1のプロセスガスを該プロセスチャンバ内に流入させることによって、非晶質シリコン膜406が該基板上に形成される。シリコンソースガスを備える第1のプロセスガス混合物と、H2及び不活性ガスを備える第1の希釈ガス混合物とを第1の温度で堆積チャンバ内に流入させることによって、多結晶シリコン膜408が該非晶質シリコン膜上に形成される。

(もっと読む)

画定された不純物勾配を有するひずみ材料層を使用する半導体構造、およびその構造を製作するための方法。

【課題】不純物の無い区域を有するひずみ材料層を含む半導体構造とデバイス、及びそれを製作するための方法を提供する。

【解決手段】ひずみ材料層104の特定の領域108は、半導体の隣接する部分から相互拡散することができる不純物を無い状態にしておく。不純物がひずみ材料層104の特定の領域108に存在する場合、デバイス性能の低下となる。説明された特徴を有する、又は説明されたステップに従って製作される半導体構造100とデバイス(例えば、電界効果トランジスタ、即ち「FET」)を使用することにより、デバイスの動作が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子形成領域間の分離絶縁膜を保護し、接合リークなしに素子と配線膜とを電気的に接続することができる半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1に形成されて素子形成領域2を画定する分離絶縁膜3と、素子形成領域2に形成された素子と、素子および分離絶縁膜3を覆うように半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5をエッチングして形成されたコンタクトホール内に埋め込まれて素子と電気的に接続する配線膜6、7とを備え、少なくとも分離絶縁膜3と層間絶縁膜5との間に、前記エッチングによる分離絶縁膜3の浸食を防止するための3層以上の絶縁膜4a、4b、4cが積層されてなる保護積層膜4が形成されていることを特徴とする半導体装置。

(もっと読む)

自然酸化物の成長を低減するためのプラズマクリーンプロセスによるパッシベーション層の形成

本明細書に記載される実施形態は、基板上の自然酸化表面を取り除くと同時に、下層の基板表面をパッシベートするための方法を提供する。一実施形態において、プロセスチャンバ内に、酸化物層を有する基板の位置決めを行い、基板の第1の温度を約80℃未満に調整し、プロセスチャンバ内において、約10以上のNH3/NF3モル比を有するアンモニア及び三フッ化窒素を含むガス混合物からクリーニングプラズマを生成し、基板上にクリーニングプラズマを凝縮することを含む方法が提供される。ヘキサフルオロ酸アンモニウムを含む薄膜が、プラズマクリーニングプロセスの間に、自然酸化物から部分的に形成される。本方法は、さらに、プロセスチャンバ内において、約100℃以上の第2の温度まで基板を加熱しつつ、基板から薄膜を取り除き、その上にパッシベーション表面を形成することを含む。  (もっと読む)

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

接点抵抗が改善された半導体構造およびその製造方法(接点抵抗が改善された半導体構造)

【課題】 構造の接点抵抗を改善した、すなわち低下させた半導体構造を提供する。

【解決手段】 自己組織化・ポリマー技術を用いて、半導体構造の導電性コンタクト領域に存在する材料内に少なくとも1つの配列されたナノサイズ・パターンを形成する。配列されたナノサイズ・パターンを有する材料は、相互接続構造または電界効果トランジスタの半導体ソースおよびドレイン領域の導電材料である。接点領域内に整列ナノサイズ・パターニング材料が存在することによって、以降の接点形成のための全領域(すなわち界面領域)が拡大し、これによって構造の接点抵抗が低下する。接点抵抗の低下により、構造を通る電流が改善する。上述のことに加えて、本発明の方法および構造では、接合領域が不変のままであるので、構造の接合容量は影響を受けない。

(もっと読む)

161 - 180 / 412

[ Back to top ]