Fターム[5F140BC17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネルの製造 (2,860) | 熱処理 (305)

Fターム[5F140BC17]に分類される特許

1 - 20 / 305

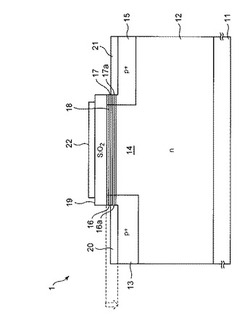

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング素子として利用される高耐圧かつ低オン抵抗な半導体装置を安価に提供する。

【解決手段】第1導電型の不純物を含有し、互いに対向する第1の主面と第2の主面とを有する半導体基板と、第2導電型の不純物を第1の濃度で含有し、前記半導体基板の前記第1の主面に露出するように形成された第1の拡散領域と、前記第2導電型の不純物を前記第1の濃度よりも高い第2の濃度で含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の側方に形成された第2の拡散領域と、前記第1導電型の不純物を含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の上方に形成された第3の拡散領域と、前記第2の拡散領域と絶縁膜を介して対向する制御電極と、を備え、前記第1の拡散領域と前記第2の拡散領域とは、前記制御電極に印加される電圧に応じて制御される電流の主経路を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】レジストパターンの下地層への悪影響を及ぼすことなくスカムを最適に除去する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上に酸化膜5cを形成し、前記酸化膜5c上にフォトレジスト8を塗布し、前記フォトレジスト8を露光し、露光された前記フォトレジスト8を現像することにより前記フォトレジス8トに開口部8aを形成し、前記フォトレジスト8をマスクとして、前記酸化膜5cを酸素プラズマ処理し、前記酸素プラズマ処理の後、前記酸化膜5cと前記フォトレジスト8に希釈フッ酸を供給し、前記希釈フッ酸を供給する工程の後、前記フォトレジスト8をマスクとして前記酸化膜5cを通して記半導体基板1に一導電型不純物をイオン注入する工程を含む。

(もっと読む)

半導体装置

【課題】長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に前記第1トレンチ領域の長さ方向の両端に接して設けられた第2トレンチ領域014および第3トレンチ領域015と、トレンチ領域に形成された第2導電型のウェル領域005と、前記第1トレンチ領域に設けられたゲート絶縁膜004と、前記ゲート絶縁膜上に接して設けられたゲート電極003と、前記第1トレンチと前記第2トレンチ領域と前記第3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体シリコン膜及び半導体デバイス、並びにそれらの製造方法

【課題】本発明の目的は、新規な半導体シリコン膜及びそのような半導体シリコン膜を有する半導体デバイス、並びにそれらの製造方法を提供することである。

【解決手段】本発明の半導体シリコン膜(160)は、複数の細長シリコン粒子(22)が短軸方向に隣接してなる半導体シリコン膜である。ここでは、細長シリコン粒子(22)は、複数のシリコン粒子の焼結体である。また、このような半導体シリコン膜(160)を製造する本発明の方法は、第1のシリコン粒子分散体を、基材(100)上に塗布し、乾燥し、光(200)を照射して、第1の半導体シリコン膜(130)を形成する工程、第2のシリコン粒子分散体を、第1の半導体シリコン膜(130)に塗布し、乾燥し、光(200)を照射する工程を含む。ここで、この方法では、第1のシリコン粒子分散体の第1のシリコン粒子の分散が5nm2以上である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜に劣化が生じることを抑制する。

【解決手段】ハードマスクを用いて素子分離溝102を形成した後、素子分離溝102に素子分離膜20を埋め込む。次いで、ハードマスクの窒化シリコン膜210を除去する。次いで、ハードマスクの表面酸化膜200を薄くする。その後、シリコン基板100を熱酸化することにより、表面酸化膜を厚くして再酸化膜202を形成する。次いで、第1素子形成領域101及び第2素子形成領域103に位置するシリコン基板に、再酸化膜202を介してチャネル不純物を注入する。次いで、再酸化膜202を除去する。次いで、第1素子形成領域101に位置するシリコン基板100に、ゲート絶縁膜110及びゲート電極120を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

1 - 20 / 305

[ Back to top ]