Fターム[5F140BF33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 結晶性、結晶粒径 (224)

Fターム[5F140BF33]の下位に属するFターム

アモルファス、非晶質 (144)

Fターム[5F140BF33]に分類される特許

61 - 80 / 80

半導体装置及びその製造方法

【課題】素子間における特性のミスマッチが少ない半導体装置を提供する。

【解決手段】基板1の上に形成した絶縁膜2の上に、平均粒径が0.02μm以上0.35μm以下であるシリコン結晶粒10を有するポリシリコン層3を形成した。不純物をイオン注入にてポリシリコン層3に導入した後に、熱処理することによりIPO酸化を行い、ポリシリコン層3の表面にIPO酸化膜4を形成し、さらにIPO酸化膜4の上に第二のポリシリコン層を形成した。そして、レジストマスクパターンによりエッチングして、ポリシリコン層3の一部で、MOSトランジスタ7のゲート電極7a及び容量素子8の下部電極8aを構成した。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物からなるゲート電極の抵抗ばらつきの発生を抑制できる半導体装置の製造方法を実現すること。

【解決手段】半導体装置の製造方法は、半導体基板200上にゲート絶縁膜201を形成する工程と、前記ゲート絶縁膜上に、金属と半導体との化合物からなり、所定のゲート長を有するゲート電極206を形成する工程とを含む半導体装置の製造方法であって、前記ゲート電極206を形成する工程は、平均粒径が前記所定のゲート長に対応した所定値以下に制御され、かつ、シリコンおよびゲルマニウムの少なくとも一方を含む、多結晶の半導体膜205を形成する工程と、前記半導体膜205上に金属膜203を形成する工程と、熱処理により前記半導体膜205と前記金属膜203とを反応させ、前記半導体膜205の全体を金属半導体化合物層に変える工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜とシリサイドゲート電極の組み合わせ技術におけるしきい値制御の問題を解決し、高性能で信頼性に優れた半導体装置を提供する。

【解決手段】シリコン基板上に、ゲート絶縁膜とこのゲート絶縁膜上に設けられたゲート電極とを有する電界効果トランジスタを備えた半導体装置において、高誘電率絶縁膜(例えばHfSiON膜)を含むゲート絶縁膜を用い、高誘電率絶縁膜に接するように下層側に設けられた、第1の金属M1(例えばNi)、M1と異なる仕事関数をもつ第2の金属M2(例えばW)およびシリコン(Si)を含むシリサイドからなる第1の層領域と、第1の層領域に接する上層側に設けられたM1(例えばNi)およびSiを含むシリサイドからなる第2の層領域とを有するゲート電極を用いる。

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁層や半導体層を備えた高品質のMOS型半導体等の電子デバイス材料の製造方法。

【解決手段】単結晶シリコンを主成分とする被処理基体上にCVD処理を施して絶縁膜を形成する工程と、前記被処理基体を、複数のスロットを有する平面アンテナ部材(SPA)を介して処理ガスにマイクロ波を照射することにより生成したプラズマに晒し、このプラズマを用いて前記絶縁膜を改質する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 しきい値電圧のばらつきの少ないゲート電極を有するCMOSデバイスを備えた半導体装置を提供することを可能にする。

【解決手段】 半導体基板に設けられた第1導電型チャネルMISトランジスタと、半導体基板に設けられた第2導電型チャネルMISトランジスタと、を備え、第2導電型チャネルMISトランジスタのゲート電極中の、ゲート絶縁膜との界面から膜厚方向に少なくとも1nm以下の領域での酸素濃度は1020cm−3以上、1022cm−3以下である。

(もっと読む)

高誘電率膜上のシリコンオキサイドキャップ

【課題】高kゲート絶縁膜上のドープされたシリコンゲート間に短絡をもたらす欠陥、トラッピングを回避する、前記高kゲート絶縁膜および前記高kゲート絶縁膜上のシリコンオキサイド膜の製造法を提供する。

【解決手段】原子層堆積プロセスを用いて基板上に高kゲート絶縁材料を堆積することを包含する、半導体基板上に集積回路構造を形成するための方法。シリコンオキサイドキャッピング層は、高速熱化学蒸着プロセスにおいてゲート絶縁材料上に堆積される。ゲート電極は、シリコンオキサイドキャッピング層上に形成される。

(もっと読む)

自己整合され積極的にスケーリングされたCMOSデバイスにおけるゲート電極の金属/金属窒化物二重層のCMOS構造体及び半導体構造体

【課題】 低仕事関数金属の不適切な熱安定性のために、nFET仕事関数とpFET仕事関数との両方を適正にするために用いることができるゲート・スタックを有するCMOS構造体を提供すること。

【解決手段】 本発明は、半導体基板の1つの領域上に配置された少なくとも1つのnMOSデバイスと、半導体基板の別の領域上に配置された少なくとも1つのpMOSデバイスとを含む、CMOS構造体に向けられる。本発明によれば、少なくとも1つのnMOSデバイスは、ゲート誘電体と、4.2eV未満の仕事関数を有する低仕事関数の元素状金属と、その場金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを含み、少なくとも1つのpMOSデバイスは、ゲート誘電体と、4.9eVより大きい仕事関数を有する高仕事関数の元素状金属と、金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを有する。本発明はまた、こうしたCMOS構造体を製造する方法も提供する。

(もっと読む)

半導体素子を形成する方法

【課題】 ゲートリーク電流の低減。

【解決手段】 本発明による半導体の製造方法は、基板を設ける工程と、誘電体層を基板の上に形成する工程と、アモルファス半導体層を誘電体層の上に成長させる工程と、アモルファス半導体層に不純物をドープする工程と、そして高温処理工程をアモルファス層に施して前記アモルファス半導体から結晶化層を形成する工程とを備える。

(もっと読む)

絶縁ゲート型半導体装置の製造方法

【課題】 絶縁ゲート型半導体装置の製造方法に関し、ゲート電極を簡単な製造工程で結晶性の高い単結晶半導体で構成する。

【解決手段】 貼り合わせ用単結晶半導体基板4に剥離用元素5をイオン注入したのち、貼り合わせ用単結晶半導体基板4のイオン注入側が貼り合わせ面となるように絶縁膜3を形成した素子形成用単結晶半導体基板1に貼り合わせ、次いで、熱処理を行って貼り合わせ用単結晶半導体基板4を注入した元素の濃度ピーク位置近傍で剥離したのち、素子形成用単結晶半導体基板1側に残存した貼り合わせ用単結晶半導体基板4の残部6をゲート電極状にエッチングする。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

歪み完全空乏型シリコン・オン・インシュレータ半導体デバイスおよびこの製造方法

絶縁体(104)上に半導体層(106)を備える、その上に絶縁体(104)を有する半導体基板(102)を提供する。半導体層(106)に歪みを引き起こす深いトレンチ分離(108)を形成する。半導体層(106)上にゲート絶縁体(202)およびゲート(204)を形成する。ゲート(204)の周りにスペーサ(304)を形成し、スペーサ(304)の外側の半導体層(106)および絶縁体(104)を除去する。スペーサ(304)の外側にくぼんだソース/ドレイン(402)を形成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体装置の製造方法

【課題】 サリサイド工程で形成されるシリサイド層のシート抵抗ばらつきを抑制する。

【解決手段】 サリサイド工程の際にCo膜上に堆積されるTiN保護膜の膜厚を、ナノグレイン構造あるいはアモルファス構造を有するように減少させる。前記TiN保護膜として、Tiに富む組成の膜を使う。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたCMOS半導体装置に適したpMOSとnMOSにおいてそれぞれ適切に制御されたGe濃度分布及び形状を有するSi/SiGeゲート電極構造を備えた半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に形成された絶縁膜と、前記絶縁膜上に形成され、前記絶縁膜との界面近くで高いゲルマニウム濃度を有し、その反対側表面で低いゲルマニウム濃度を有する第1のゲート電極と、前記絶縁膜上に形成され、電極中でほぼ一様なゲルマニウム濃度を有し、6×1020atoms/cm3以上の濃度のn型不純物を有する第2のゲート電極とを具備する。

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

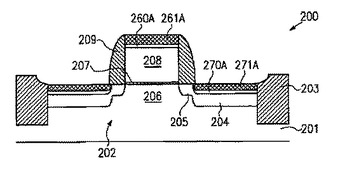

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

キャリア移動度を増加させた電界効果トランジスタ

ある例示的な実施形態によれば、基板(104)上に位置するFETは、基板(104)中に位置するチャネル(112)を含んでいる。このFETはさらに、チャネル(112)上に位置する第1ゲート絶縁層(116)を含んでいる。この第1ゲート絶縁層(116)は、第1熱膨張係数を有している。FETはさらに、第1ゲート絶縁層(116)上に位置する第1ゲート電極(114)を含んでいる。この第1ゲート電極(114)は、FET中のキャリア移動度を増加させるように、第1熱膨張係数と異なる第2熱膨張係数を有している。この第2熱膨張係数は、例えば第1熱膨張係数よりも大きくされている。キャリア移動度の増加は、例えばチャネル(112)中に生成された引っ張り歪みにより引き起こされる。  (もっと読む)

(もっと読む)

61 - 80 / 80

[ Back to top ]