Fターム[5F140BF34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 結晶性、結晶粒径 (224) | アモルファス、非晶質 (144)

Fターム[5F140BF34]に分類される特許

41 - 60 / 144

半導体素子およびその製造方法

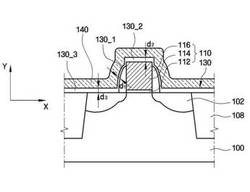

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細ショットキーMISFETのソース電極がチャネル端の表面ポテンシャルをピニングすることで発生するトランジスタ性能の劣化を防止する。

【解決手段】ショットキーMISFETを構成する、半導体基板上に形成したソース金属電極8と半導体基板中のチャネル領域11との接触で形成されるショットキー障壁高さとφB0、半導体基板のバンドギャップEGと、半導体基板の真性キャリア濃度niと、デバイスの動作温度Tと、ボルツマン係数kに対して、少なくともソース電極と接するチャネル端近傍の不純物濃度NCHを、NCH≦ni・exp((qφB0−0.5EG)/kT)の条件を満たすようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置の製造方法

【課題】MOS構造の半導体装置において、ゲート電極をイオン注入のチャネリングに対して強い構造とする。

【解決手段】半導体基板上でゲート絶縁膜の上に半導体材料を堆積してゲート電極を形成する。このゲート電極の表面または内部に非晶質層を形成する。その後、ゲートサイドウォールを形成し、ゲート電極およびサイドウォールをマスクとして半導体基板に不純物をイオン注入し、ソース/ドレインを形成する。非晶質層としては、窒素を1×1020〜1×1022/cm3個含む層を形成する。これを、熱処理に対する不純物析出抑制層とし、イオン注入に対するチャネリング防止層とする。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】トリミングを用いず、プロセスの大幅な変更や工程数を大きく増加させずに、高精度に微細化してゲート電極または配線を形成できる半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10のチャネル形成領域上にゲート絶縁膜12を形成し、その上層に第1導電層20を形成し、第1導電層にゲート電極のパターンに対応し第1の幅20wを有する第1凹部20tを形成し、その内壁を被覆して、第1の幅より狭い第2の幅31wの第2凹部31tを有する第2導電層31を形成し、第2凹部を埋め込んでマスク層32を形成し、第1凹部の外部における第2導電層及びマスク層を除去し、第1凹部に残されたマスク層をマスクとして第2導電層及び第1導電層をパターン加工してゲート電極Gを形成し、ゲート電極Gの両側部における半導体基板中にソース・ドレイン領域13を形成する。

(もっと読む)

半導体装置

【課題】ゲート、ソースドレインの寄生抵抗の低減、ソースドレインの寄生容量の低減、パンチスルーやDIBLによるリークの低減を同時に実現する。

【解決手段】半導体基板10の表面に第1の素子分離領域11bが形成されている。第1導電型領域12及び第2導電型領域13は、半導体基板10の表面に形成され、第1の素子分離領域11bにより分離されている。第1のゲート電極15a,16aが第1導電型領域12及び第2導電型領域13上にそれぞれ形成されている。拡散領域24a,24b,25a,25bが、第1導電型領域12及び第2導電型領域13の表面にそれぞれ形成されている。第1のシリサイド膜31a,31bが第1のゲート電極15a,16aの上層部に形成されている。第2のシリサイド膜30cは、拡散領域24a,24b,25a,25b上に形成され、下面が基板10の上面と同一面上にある。

(もっと読む)

半導体素子及びそのゲート形成方法

【課題】高誘電定数を有する物質からなるゲート絶縁膜を有する半導体素子及びそのゲート形成方法を提供する。

【解決手段】素子分離膜202によりアクティブ領域が画定されている半導体基板200を提供する段階と、前記アクティブ領域上にゲート絶縁膜204を形成する段階と、前記ゲート絶縁膜204上にキャッピング膜206を形成する段階と、前記キャッピング膜206及び前記ゲート絶縁膜204を有する半導体基板200に対してアニール工程を施す段階と、前記アクティブ領域の一部にフルシリサイドゲート208を形成する段階とを含む。

(もっと読む)

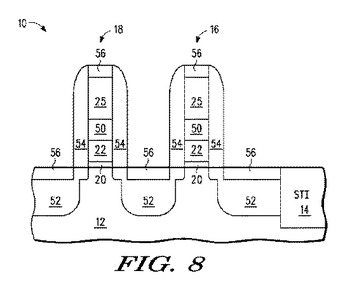

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】半導体基板1にSTI法で素子分離領域4を形成し、ゲート絶縁膜7を形成し、ゲート電極8a,8bを形成し、ソース・ドレイン用のn+型半導体領域9bおよびp+型半導体領域10bを形成し、半導体基板1上に金属膜12を形成し、金属膜12上にバリア膜13を形成する。それから、第1の熱処理を行って金属膜12とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させて金属シリサイド層を形成してから、バリア膜13および未反応の金属膜12を除去し、前記金属シリサイド層を残す。素子分離領域4は半導体基板1に圧縮応力を作用させる。バリア膜13は半導体基板1に引張応力を生じさせる膜であり、第1の熱処理では、金属膜12を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層が形成される。

(もっと読む)

半導体装置の製造方法

【課題】シリコンから構成される導電パターンの下から上までの幅を均一化すること。

【解決手段】半導体基板1上に絶縁膜5を介して第1シリコン膜6を形成し、第1シリコン膜6に高濃度で一導電型不純物を導入し、第1シリコン膜6上に第2シリコン膜9を形成し、第2シリコン膜9上に所定パターンのマスク10mを形成した後、マスク10mから露出する領域で、第1シリコン膜6が露出しない深さまで第1条件により第2シリコン膜9をエッチングし、ついで第1条件に比べて半導体基板1の垂直方向へのエッチング成分の高い第2条件によって第2シリコン膜9の残りと第1シリコン膜6を絶縁膜5が露出しない深さまでエッチングし、さらに第2条件に比べて絶縁膜に対する第1シリコン膜6のエッチング選択比が大きな第3条件により第1シリコン膜6の残りをエッチングする工程とを有している。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETおよびPMOSFETに適した組成のフルシリサイド相を、少ない工程数で、容易に得ることが可能な製造方法を提供すること。

【解決手段】基板1上に、ゲート絶縁膜2を介して前記NMOSFET用第1ゲート電極、およびPMOSFET用第2ゲート電極を形成する工程と、前記ゲート電極を覆う層間膜8を形成する工程と、前記層間膜8を平坦化し、前記第1、第2ゲート電極のシリコン層3を露出する工程と、前記第2ゲート電極の上部を選択的に除去する工程と、前記第2のゲート電極および第1のゲート電極のシリコン層3上に金属膜11を形成し、シリサイド化熱処理を行う工程と、熱処理工程後に未反応の金属膜を除去する工程と、を含み、第2のゲート電極上部を選択的に除去する工程の前に、前記第1および第2のゲート電極の各シリコン層3に、シリサイド相の組成制御のための不純物を同時に導入する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化が進みゲート長のバリエーションが増大した場合にも、高駆動力MISFETを搭載した高性能デバイスを安定して実現できる簡便なFUSI化技術を提供する。

【解決手段】第1のゲート長(相対的に短いゲート長)を持つ第1のゲート電極105Aがフルシリサイド化されているのに対して、第2のゲート長(相対的に長いゲート長)を持つ第2のゲート電極105Bはフルシリサイド化されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に複数の半導体素子を有する半導体装置を少ない工程で簡単に製造する。

【解決手段】アナログ回路素子領域25におけるシリコン酸化膜26の表面への窒素導入と、デジタル回路素子領域24におけるシリコン窒化膜27の形成とを、プラズマ窒化法によって同一の工程で行う。そのため、デジタル回路素子領域24のゲート電極パターンとアナログ回路素子領域25のゲート電極パターンとを、同一のフォトリソグラフィ工程によって形成することが可能になる。したがって、互いに異なる組成を有する2つのゲート絶縁膜上の夫々にゲート電極パターンを形成して成る2つのMOS半導体素子を、少ない工程で簡単に形成することができる。また、工程が少ない分だけ加工精度を高めることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】金属シリサイド層によるゲートエッジ部でのリーク電流を低く抑えると共に、ストレッサを形成可能なゲート間のスペースを確保する。

【解決手段】MOS構造素子の形成後に、シリサイド反応のバリアとして機能可能なメタル膜でシリサイド防止膜を形成する。当該メタル膜は、ドライエッチングで容易にエッチングされる材料から成り、且つ、サリサイドプロセス中の酸系の混合溶液に可溶な材料から成る。シリサイド形成領域開口のために、レジストマスクを利用してメタル膜をドライエッチングする。その結果、ドライエッチングの終了後に、当該メタル膜より成る第2サイドウォールスペーサー9Mが形成される。その後、サリサイドプロセスを実行して金属シリサイド層12を形成する。その際、サリサイドプロセスの過程で未反応の金属を除去する際に、第2サイドウォールスペーサー9Mは同時に除去される。

(もっと読む)

半導体素子の製造方法、半導体素子、及び遅延装置

【課題】トランジスタのゲート領域にWSi2が積層されたノンドープのポリシリコンを用い、WSi2をゲート電極とし、ノンドープのポリシリコンを高抵抗体として扱い、実効的なゲート絶縁部の膜厚を制御しローパスフィルターを形成する技術がある。この技術をサリサイド工程に展開する場合に、例えばLDD形成に伴い寄生的に当該ポリシリコンの一部に不純物が添加されると、サリサイド化に伴う高速の拡散により広がり、当該ポリシリコンの比抵抗が低下しフィルター特性が劣化するという課題がある。

【解決手段】トランジスタのゲート領域形成前にLDD部を形成する。LDD部を先に形成することで、ゲート領域とLDD部とのオーバーラップがある状態で、かつゲート領域への不純物導入を防止することが可能となる。LDD部の形成に伴う不純物がゲート領域に侵入しないため、高速の拡散が生じてもゲート領域内への不純物拡散が防止できる。

(もっと読む)

ゲート構造を有する半導体素子及びその製造方法

【課題】ゲートコンタクト抵抗値及びシート抵抗値を同時に低くし得る中間構造物を有するゲート構造及びゲート構造を有する半導体素子、並びにそれらの製造方法を提供すること。

【解決手段】本発明の半導体素子は、上面及び下面を有する基板21と、基板21の上面近くに形成され、ゲート絶縁膜22、ゲート絶縁膜22上に形成された第1電極23、第1電極23上に形成された中間構造物24、及び中間構造物24上に形成された第2電極25を含むゲート構造とを備え、中間構造物24が、チタン(Ti)を含む第1Ti膜101と、タングステン及びシリコンを含み、第1Ti膜上に形成された第2W膜24Dとを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上にダミーゲート層を形成する工程と、前記ダミーゲート層の側面に、ダミーゲート層を構成する材料との間で、エッチング選択性を有する側壁絶縁膜を形成する工程と、全面に層間絶縁膜を堆積する工程と、前記層間絶縁膜を、前記ダミーゲート層の上面が露出するまで除去する工程と、前記ダミーゲート層を除去し、溝を形成する工程と、前記溝の底面にゲート絶縁膜を形成する工程と、底面にゲート絶縁膜が形成された前記溝内にゲート電極を形成する工程とを具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上に、ゲート絶縁膜及びゲート電極を設け、それらの側面にダミー側壁を形成し、その周囲を層間絶縁膜で囲み、前記ゲート電極及びダミー側壁の上面が露出する構造を提供する工程と、

前記ダミー側壁を除去して空洞を形成する工程と、

前記空洞内を側壁材料で埋め、側壁を形成する工程と

を具備する半導体装置の製造方法。

(もっと読む)

41 - 60 / 144

[ Back to top ]