Fターム[5F140BF34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 結晶性、結晶粒径 (224) | アモルファス、非晶質 (144)

Fターム[5F140BF34]に分類される特許

121 - 140 / 144

半導体装置およびその製造方法

【課題】ゲート電極に含まれる不純物に起因した品質の低下が抑制された高品質の半導体装置およびその製造方法を得ること。

【解決手段】半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、不純物が導入された複数の半導体膜が積層されてなるゲート電極と、を備え、前記ゲート電極は、前記不純物の不純物濃度プロファイルが前記複数の半導体膜の各層において急峻なピークを有し、前記絶縁膜上に形成された最下層の前記半導体膜の前記絶縁膜近傍における不純物濃度が他の前記半導体膜の不純物濃度よりも小とされている。

(もっと読む)

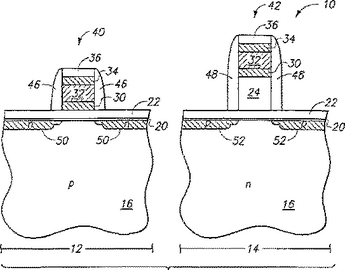

スケーラブル集積論理および不揮発性メモリ

スケーラブル論理トランジスタはドレインおよびソースのための一組のドープされた領域を有する。ゲート絶縁層は基板上でドレイン領域とソース領域の間に形成される。ゲートスタックは、ポリシリコンや金属のようなゲート層を、二つの窒化金属層の間に置くことで形成される。また、埋め込まれた金属ナノドット層を有する高K誘電率膜を、トンネル絶縁層とゲートスタックとの間に設けるようにして付加することによって、この基本的構成から互換性のある不揮発性メモリトランジスタを形成することもできる。 (もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率膜を含むゲート絶縁膜を有するMISトランジスタを有する半導体装置及びその製造方法に関し、ポリシリコンの異常成長やゲートリーク電流を抑制しうる半導体装置の構造及びその製造方法を提供する。

【解決手段】 半導体基板10に形成され、ハフニウム組成xが0.7<x<1であるHfxAl1−xOyよりなる誘電体膜16と、誘電体膜16上に形成され、誘電体膜16とは異なる誘電体膜18とを有するゲート絶縁膜20と、ゲート絶縁膜20上に形成され、ポリシリコン膜を有するゲート電極24とを有する。これにより、ポリシリコン膜の形成過程における局所的な異常成長が防止される。また、ゲートリーク電流を大幅に低減することができる。

(もっと読む)

半導体構造およびそれを形成する方法(金属酸化物の付着を介して形成されたしきい電圧制御層を含む窒素含有電界効果トランジスタ・ゲート・スタック)

【課題】 ゲート誘電体とゲート電極との間にVt安定化層を含む半導体構造を提供することにある。

【解決手段】 Vt安定化層は、構造のしきい電圧およびフラットバンド電圧を目標値に安定化することができ、窒化金属酸化物または窒素なし金属酸化物を含み、Vt安定化層が窒素なし金属酸化物を含む条件で半導体基板またはゲート誘電体のうちの少なくとも一方が窒素を含む。また、本発明は、このような構造を形成する方法も提供する。

(もっと読む)

ニッケルシリサイド膜の形成方法、半導体装置の製造方法およびニッケルシリサイド膜のエッチング方法

基板シリコン中のシリコン原子の消費量をできるだけ少なくして、なおかつ十分な厚さをもった低抵抗のニッケルシリサイド膜の形成方法、半導体装置の製造方法およびニッケルシリサイド膜のエッチング方法を提供する。表面に半導体領域および絶縁膜領域を有する基板上に、シリサイド反応を起こさない第1の基板温度で少なくとも各1層よりなるニッケル層とシリコン層を交互に積層する積層膜形成工程と、その積層膜をニッケルモノシリサイドが生成する第2の基板温度で熱処理するシリサイド反応工程と、ウェットエッチングによって絶縁膜上に形成された膜を除去する工程とを含む半導体装置の製造方法であって、積層膜形成工程において、積層膜全体のシリコン原子数に対するニッケル原子数の比を1または1より大きくすることによって、上記課題を解決した。  (もっと読む)

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

歪み完全空乏型シリコン・オン・インシュレータ半導体デバイスおよびこの製造方法

絶縁体(104)上に半導体層(106)を備える、その上に絶縁体(104)を有する半導体基板(102)を提供する。半導体層(106)に歪みを引き起こす深いトレンチ分離(108)を形成する。半導体層(106)上にゲート絶縁体(202)およびゲート(204)を形成する。ゲート(204)の周りにスペーサ(304)を形成し、スペーサ(304)の外側の半導体層(106)および絶縁体(104)を除去する。スペーサ(304)の外側にくぼんだソース/ドレイン(402)を形成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 サリサイド工程で形成されるシリサイド層のシート抵抗ばらつきを抑制する。

【解決手段】 サリサイド工程の際にCo膜上に堆積されるTiN保護膜の膜厚を、ナノグレイン構造あるいはアモルファス構造を有するように減少させる。前記TiN保護膜として、Tiに富む組成の膜を使う。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたCMOS半導体装置に適したpMOSとnMOSにおいてそれぞれ適切に制御されたGe濃度分布及び形状を有するSi/SiGeゲート電極構造を備えた半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に形成された絶縁膜と、前記絶縁膜上に形成され、前記絶縁膜との界面近くで高いゲルマニウム濃度を有し、その反対側表面で低いゲルマニウム濃度を有する第1のゲート電極と、前記絶縁膜上に形成され、電極中でほぼ一様なゲルマニウム濃度を有し、6×1020atoms/cm3以上の濃度のn型不純物を有する第2のゲート電極とを具備する。

(もっと読む)

ポリシリコンゲルマニウムゲートスタック及びその形成方法

従来のCMOSゲートスタックと比べて反転キャパシタンスを増大させるCMOSゲートスタックが記載される。ゲート誘電体層に近い従来のポリSiゲートの代わりに、ポリSiGeゲートを用いて、活性化され得る埋込まれたドーパント量を増加させる。この増加は、従来のCMOSゲートスタックにおける反転キャパシタンスを制限するポリシリコンの枯渇を克服する。ポリSiGe層をゲートスタックに組込むために、ゲート誘電体層とポリSiGe層との間にSi薄層を堆積させる。適切なサリサイド形成を確実にするために、ポリSiGe層の上にポリSi層のキャップを被せる。ポリSiGeの上に微粒子のポリSiを得るために、ポリSi層とポリSiGe層の間に第2のSi層を堆積させる (もっと読む)

SEG膜により拡張した接合領域を有する半導体素子及びその製造方法

【課題】 漏れ電流の増加なしに接合領域の面積を拡張させ、素子分離のための絶縁効果を最大化できるSEG膜により拡張した接合領域を有する半導体素子及びその製造方法を提供する。

【解決手段】 基板上に拡張したフィン状の突出部の上部の側壁を取り囲むSEG膜をエッチングして、ゲートパターンが形成される突出部のチャンネル領域の側壁を露出させた後、チャンネル領域の少なくとも一つの側壁を覆うゲートパターンを形成するSEG膜により拡張した接合領域を有する半導体素子及びその製造方法である。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

絶縁ゲート型電界効果トランジスタの製法

【課題】微細なゲート電極を有するLDD(Lightly Doped Drain)構造の絶縁ゲート型電界効果トランジスタを製造する方法において、製造歩留りを向上させる。

【解決手段】P型ウェル領域14の表面に素子孔を有するフィールド絶縁膜16を形成した後、素子孔内の半導体表面にゲート絶縁膜20を形成する。絶縁膜20の上に破線で示すようにポリシリコン等のゲート電極層24を形成した後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN+型ソース領域28及びN+型ドレイン領域30を形成する。等方性エッチング処理により電極層24を実線で示すように細く且つ薄くした後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN−型ソース領域32及びN−型ドレイン領域34を形成する。

(もっと読む)

シリサイド領域を有する半導体デバイスの製造方法

【課題】本発明は、半導体デバイスの製造方法及び半導体デバイスを含む集積回路の製造方法を提供する。

【解決手段】本発明の半導体デバイス(100)を製造する方法は、とりわけ、基板(110)上にゲート構造(120)を形成するステップオ、及びゲート構造(120)の近くの基板(110)にソース/ドレイン領域(190)を形成するステップを含む。本方法は、更に、ゲート構造(120)及び基板(110)をドライエッチングするステップ、及びゲート構造(120)及び基板(110)をドライエッチングするステップに続いて、ソース/ドレイン領域にフッ素を配置して、フッ化したソース/ドレインを形成するステップを含む。その後、本方法は、ゲート構造(120)とフッ化したソース/ドレインに金属スイサイド領域(510,520)を形成するステップを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 低コストで歩留り良く製造でき、ゲート絶縁膜の信頼性が高く、しきい値電圧のばらつきが小さい半導体装置及びその製造方法を提供する。

【解決手段】 金属シリサイド膜4は、ゲート絶縁膜3上にアモルファスSi膜、金属膜及びSi膜5を順次形成し、熱処理によって金属膜をシリサイド化することにより得られる。金属膜の上にSi膜5を形成し、ゲート電極のゲート絶縁膜3側からのシリサイド化反応により金属シリサイド膜4を形成するため、不純物イオンがゲート電極とゲート絶縁膜3との界面に濃縮することが無い。これにより、不純物イオンのゲート絶縁膜3中又はチャネル領域への拡散を抑制し、MISFETのしきい値のばらつきを低減できる。また、ゲート絶縁膜3とゲート電極との界面における不純物の偏析を抑制し、ゲート電極の剥離を防止することができるため、ゲート絶縁膜3の信頼性が高い。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜としてhigh−k膜を適用し、ゲート電極としてポリシリコン膜を適用したトランジスタのしきい値電圧の上昇を抑制し、所望の駆動能力が得られる半導体装置と、その製造方法を提供する。

【解決手段】 トランジスタTのゲート電極5aは、シリコンを含有するポリシリコン膜から形成されている。トランジスタTのゲート絶縁膜4は、HfSiO膜2aとそのHfSiO膜上に形成されたシリコン酸化膜3aから形成されている。シリコン酸化膜3aは、ゲート電極5aが含有するシリコンと金属シリサイド化反応が起こらないように金属元素を含有していない。シリコン酸化膜3aは、HfSiO膜2aが含有するHfとゲート電極5aが含有するシリコンとの反応を阻止する保護膜としての機能を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

121 - 140 / 144

[ Back to top ]