Fターム[5F140BG31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644)

Fターム[5F140BG31]の下位に属するFターム

イオン注入 (445)

Fターム[5F140BG31]に分類される特許

161 - 180 / 199

半導体装置及びその製造方法

本発明によれば、シリコン基板と、このシリコン基板上にシリコン含有絶縁膜を介して設けられた高誘電率金属酸化膜を有するゲート絶縁膜と、このゲート絶縁膜上に形成されたシリコン含有ゲート電極と、このゲート電極の側面側に酸化シリコンを構成部材として含むサイドウォールとを有し、このサイドウォールと少なくとも前記ゲート電極の側面との間に窒化シリコン膜が介在するMIS型電界効果トランジスタを備えた半導体装置が提供される。この半導体装置は、ゲート長が短い微細構造を有しながら、低消費電力でかつ高速動作が可能となる。  (もっと読む)

(もっと読む)

半導体基板のインサイチュ洗浄方法及びこれを採用する半導体素子の製造方法

【課題】半導体基板のインサイチュ洗浄方法及びこれを採用する半導体素子の製造方法を提供する。

【解決手段】一実施例によるエピタキシャル層の製造方法は反応チャンバ内に露出した半導体表面を有する基板をローディングさせるステップを具備する。前記露出した半導体表面上に存在する酸化物が分解されて酸素を除去する洗浄条件が成立するように前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱する。前記酸化物が除去されるように前記洗浄条件を洗浄時間の間に維持して清浄な半導体表面を形成する。前記清浄な半導体の表面上にエピタキシャル層を形成する。前記基板を前記反応チャンバからアンローディングさせる。

(もっと読む)

半導体装置とその製造方法

【課題】 絶縁性金属酸化膜をゲート絶縁膜に使用したMOSトランジスタの特性を向上させることができる半導体装置とその製造方法を提供すること。

【解決手段】シリコン(半導体)基板1と、シリコン基板1の上に形成され、絶縁性金属酸化物で構成されるゲート絶縁膜14と、ゲート絶縁膜14の上に形成され、シリコンを含有するゲート電極18と、ゲート電極18の側方のシリコン基板10に形成され、ゲート絶縁膜14とゲート電極18と共にMOSトランジスタTR1を構成するソース/ドレイン領域22とを有し、ゲート電極18の少なくとも下面に鉄族元素を拡散させたことを特徴とする半導体装置による。

(もっと読む)

半導体集積回路

【課題】ソース電位(VSS)との間に低不純物濃度のウェル領域を具備することにより、容量素子と他の回路素子との容量結合を抑制する。

【解決手段】N型の基板10上にP型のウェル領域11とN型のウェル領域12を形成する。N型ウェル領域12の表面にゲート電極14、ソース・ドレイン領域13、N型の拡散領域15を形成し、ゲート酸化膜16を誘電体として容量素子を形成する。P型のウェル領域11にはソース電位(VSS)を印加する。ゲート電極14を一方の端子Aとし、ソース・ドレイン領域13とN型の拡散領域12とを他方の端子Bとする。N型ウェル領域12とP型ウェル領域11とが低濃度PN接合となるので、他方の端子Bとソース電位(VSS)間の寄生容量を低減できる。

(もっと読む)

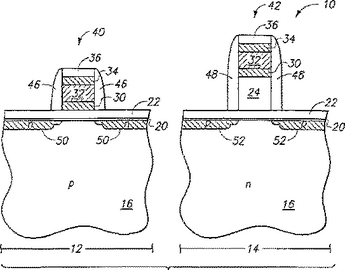

MOS型半導体装置の製法

【課題】ドレイン側のポケット領域とLDD領域との間のオフセット距離のばらつきを低減できるMOS型半導体装置の製法を提供する。

【解決手段】半導体基板10の表面に形成したフィールド絶縁膜12の素子孔内にゲート絶縁膜14を形成した後、絶縁膜14及び12の上にドープトポリシリコン等からなるゲート電極層16及びキャパシタ用電極層18をそれぞれ形成する。絶縁膜12及び電極層16をマスクとするイオン注入処理によりポケット領域20,22を形成した後、電極層16,18を覆ってキャパシタ用絶縁層26をCVD法等により形成する。絶縁層26を介してのイオン注入処理により低濃度ソース、ドレイン領域28,30を形成する。ポケット領域22とLDD領域30との間のオフセット距離Lは、絶縁層26の厚さに対応して精度良く決定される。サイドスペーサ形成処理の後、高濃度ソース,ドレイン領域を形成する。

(もっと読む)

MOS型半導体装置の製法

【課題】低ノイズで特性変動の少ないMOS型半導体装置の製法を提供する。

【解決手段】シリコン基板10の一方の主面には、ゲート絶縁膜14、ゲート電極層16、ソース領域24及びドレイン領域26を有するMOS型トランジスタを形成した後、このトランジスタを覆って層間絶縁膜28を形成する。ホトリソグラフィ及びドライエッチング処理によりソース領域24及びドレイン領域26にそれぞれ対応する接続孔32及び34を絶縁膜28に形成した後、接続孔32及び34をそれぞれ介してソース領域24及びドレイン領域26にフッ素イオンF+を注入する。この後、ソース領域24及びドレイン領域26中のフッ素を熱処理により電極層16の下方で絶縁膜14と基板10との界面に拡散させてシリコンのダングリングボンドをフッ素原子で終端させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース・ドレイン領域におけるシリコン基板をエッチングする際にゲート電極の上部が併せてエッチングされることを防止し得る半導体装置の製造方法を得る。

【解決手段】STI分離膜2の材質、サイドウォールスペーサ9の材質、及びキャップ膜8の材質は除去されず、シリコン基板1の材質及びゲート電極7の材質は除去される条件下で、エッチングを行う。これにより、ゲート構造50及びサイドウォールスペーサ9によって覆われずに露出している部分のシリコン基板1のみが選択的に除去され、その部分におけるシリコン基板1の上面内にリセス11が形成される。ゲート電極7の上面はキャップ膜8によって覆われているため、かかるエッチングによってはゲート電極7は除去されない。

(もっと読む)

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

スケーラブル集積論理および不揮発性メモリ

スケーラブル論理トランジスタはドレインおよびソースのための一組のドープされた領域を有する。ゲート絶縁層は基板上でドレイン領域とソース領域の間に形成される。ゲートスタックは、ポリシリコンや金属のようなゲート層を、二つの窒化金属層の間に置くことで形成される。また、埋め込まれた金属ナノドット層を有する高K誘電率膜を、トンネル絶縁層とゲートスタックとの間に設けるようにして付加することによって、この基本的構成から互換性のある不揮発性メモリトランジスタを形成することもできる。 (もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】浅い高濃度のソース・ドレイン層を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコンからなる表面領域を持つ基板、表面領域上に形成されたゲート絶縁膜、ゲート絶縁膜上に形成されたゲート電極、ゲート電極の両側に設けられた側壁絶縁膜、側壁絶縁膜下からその外側に向かった部分の基板表面に形成された溝内に不純物を含むシリコン膜を堆積して形成された埋め込み形成型のソースおよびドレイン層を具備し、溝の底部のシリコン膜の不純物濃度は1×1019〜1×1022cm-3、かつ、溝の深さ方向に沿ったシリコン膜の不純物濃度は一定であり、かつ、埋め込み型形成型のソースおよびドレイン層は、側壁絶縁膜下に形成された第1の埋め込み形成型のソースおよびドレイン層、側壁絶縁膜外側に形成され、第1の埋め込み形成型のソースおよびドレイン層よりも厚い第2の埋め込み型形成型のソースおよびドレイン層を含む。

(もっと読む)

歪み完全空乏型シリコン・オン・インシュレータ半導体デバイスおよびこの製造方法

絶縁体(104)上に半導体層(106)を備える、その上に絶縁体(104)を有する半導体基板(102)を提供する。半導体層(106)に歪みを引き起こす深いトレンチ分離(108)を形成する。半導体層(106)上にゲート絶縁体(202)およびゲート(204)を形成する。ゲート(204)の周りにスペーサ(304)を形成し、スペーサ(304)の外側の半導体層(106)および絶縁体(104)を除去する。スペーサ(304)の外側にくぼんだソース/ドレイン(402)を形成する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】

ポリメタル構造のゲート電極を有するMOSFET、特に、DRAMのメモリセルトランジスタの接合リークをよりいっそう低減する。

【解決手段】

半導体基板上に、ゲート絶縁膜、ポリシリコン膜、タングステンなどの高融点金属膜、ゲートキャップ絶縁膜を順次積層し、エッチングによりゲートキャップ絶縁膜および高融点金属膜を選択的に除去する。その後、ゲートキャップ絶縁膜、高融点金属膜及びポリシリコン膜の側面に、シリコン窒化膜及びシリコン酸化膜からなる2重の保護膜を形成し、これをマスクとして用いてポリシリコン膜をエッチングする。その後、ライト酸化処理を行って、ポリシリコン膜の側面にシリコン酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】 動作時のドレイン耐圧の向上を図る半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極のドレイン電極24側の端部15aの近傍からドレイン電極24の方向(X2方向)に形成された第1ドレイン領域21と、第1ドレイン領域21の内側でドレイン電極24に接するドレインコンタクト領域23と、ドレインコンタクト領域23の周囲および下側に形成された第2ドレイン領域22とから構成し、第2ドレイン領域22の不純物濃度を第1ドレイン領域21よりも高濃度でかつドレインコンタクト領域23よりも低濃度に設定する。さらに、第2ドレイン領域22をそのゲート電極15側の端部22aがゲート電極の端部15aから所定の距離L1だけ離間した配置とする。

(もっと読む)

III−V族半導体層に上部層が積層されている構造体とその製造方法

【課題】 GaN層24の表面に上部層が積層されている構造体を製造するときに、GaN層24の表面が損傷することなく、その表面に形成されている自然酸化膜の酸化ガリウム膜を除去する。

【解決手段】 GaN層24の表面に酸化シリコンからなるSiO2層26が積層されている構造体を製造する方法であり、GaN層24の表面を非プラズマ状態のアンモニアを含むガスに曝す曝露工程と、そのアンモニアガスに曝露されたGaN層24の表面にSiO2層26を積層する積層工程を備えていることを特徴としている。

(もっと読む)

厚い歪みシリコン層を形成する方法、および厚い歪みシリコン層を組み込んだ半導体構造

シリコンゲルマニウム層(40)上に歪みシリコン層(50)を成長させ、歪みシリコン層(50)上にシリコンゲルマニウム層(52)を歪みシリコンに対して単一で連続的な原位置におけるたい積プロセスで成長させる。浅いトレンチ分離(48)を、歪みシリコン層(50)を成長させる前に下側のシリコンゲルマニウム層(40)中に形成する。この2つのシリコンゲルマニウム層(40)(52)は、歪みシリコン層(50)の引張歪みを維持するとともに、処理中の温度変化により生じ得るミスフィット転位の形成を抑制するように働く、歪みシリコン層の両面における2層基板を効果的に提供する。したがって、後の処理中に著しいミスフィット転位が生じることなく成長させることができる歪みシリコン(50)の臨界膜厚は、事実上、シリコンゲルマニウム層(40)(52)のゲルマニウム量の2倍となる。歪みシリコン層(50)を形成する前に浅いトレンチ分離(48)を形成することにより、歪みシリコン層(50)が極端な熱応力を受けないようにし、さらにミスフィット転位の形成を減少する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】スイッチング動作における駆動力を向上する。

【解決手段】基板1とドレイン領域2からなる第一導電型の半導体基体の一主面側にヘテロ半導体層30を形成する工程と、所定の開口を有するマスク層をマスクとして用いて、ヘテロ半導体層30を選択的に、かつ所定の厚みを残すようにエッチングする工程と、ヘテロ半導体層30の露出した部分を酸化する工程と、該酸化によって形成された酸化膜10をエッチングしてヘテロ半導体領域3を形成する工程と、ヘテロ半導体領域3並びに半導体基体に接するようにゲート絶縁膜4を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】導通時における駆動力を向上させる。

【解決手段】所定の開口を有するマスク層を用いて、基板1とドレイン領域2からなる半導体基体の一主面側に所定の溝15を形成する工程と、少なくとも溝15の側壁に接して、該溝15からはみ出すように埋め込み領域11を形成する工程と、半導体基体並びに埋め込み領域11に接するようにヘテロ半導体層30を形成する工程と、ヘテロ半導体層30をパターニングし、ヘテロ半導体領域3を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 ON状態/OFF状態に加えて、OFF状態よりも大きくON状態よりも小さい電流がソース/ドレイン領域間に流れるリークモードを有する半導体装置およびその製造方法を提供する。

【解決手段】 トランジスタ1は、第1と第2ゲート電極G1,G2を備える。第1と第2ゲート電極は、同一のソース/ドレイン領域を共有し、第1と第2トランジスタが形成される。第1と第2ゲート電極G1,G2にはそれぞれ独立して電圧が印加される。トランジスタ1は、少なくとも第1トランジスタがON状態である第1の状態(ON状態)と、第1と第2トランジスタG1,G2がOFF状態である第2の状態(OFF状態)と、第1トランジスタがOFF状態であり第2トランジスタがON状態である第3の状態(リークモード)とを実現する。

(もっと読む)

161 - 180 / 199

[ Back to top ]